# NCAB Group | Seminar no. 2 How to manufacture a PCB

| 42.1 General |                                       | YesorNo | Max hole | Min hol<br>size |

|--------------|---------------------------------------|---------|----------|-----------------|

|              | Detail                                | Y       | 0.6      | 0.2             |

|              | Soldermask IPC 4761 Type VI           | Y       | 0.4      | 0.25            |

|              | Resignon conductive IPC4/61 (ype 1)   | Y       | 0.4      | 0.25            |

|              | Sesin electrical conductive           | N       |          |                 |

|              | Regin thermal conductive              |         | 0.9      | 0.1             |

|              | Over plated/ capped IPC 4751 type VII | r       | 1 2.4    | -               |

4.2.2 Plug depth (solder mask IPC4761 type VI)

Emplish duignes

| Roard Thickness<br>(H)<br>Holessker(D) | 0.AmmsH<1.0mm | 1.0mmsH<1.8mm | TommsHc |  |

|----------------------------------------|---------------|---------------|---------|--|

| 0.2mmsD-0.6mm                          | A=100%        | A=100%        | A=70%   |  |

| 0.SmmcDc0.Smm                          | A=100%        | A=70%         | A≈70%   |  |

# Introduction to Multilayer PCBs

# INTRODUCTION TO MULTILAYER PCB'S What is a multilayer PCB?

- The green thing with holes in it.

- The first item needed when building any piece of electronics, but often gets ordered last.

- A platform for components.

- Circuitry with pre-defined electrical function.

Three of more conductive layers of copper which have been bonded to non-conductive substrates, yet are electrically connected where needed, so that they can electrically connect specific electronic components using tracks, pads and other features (imaged and etched to form a bespoke design) in order to fulfill a **specific** function.

### INTRODUCTION TO MULTILAYER PCB'S History of PCBs

- 1903 First PCB-patent

- 1903-1946 Single / double sided boards (NPTH)

- 1947 Double sided, plated through holes developed

- 1960 Multilayer process developed.

- 1993 NCAB was founded (1986 in Malaysia)

- 1995 Micro via production

- 2000 Embedded components

# Manufacturing

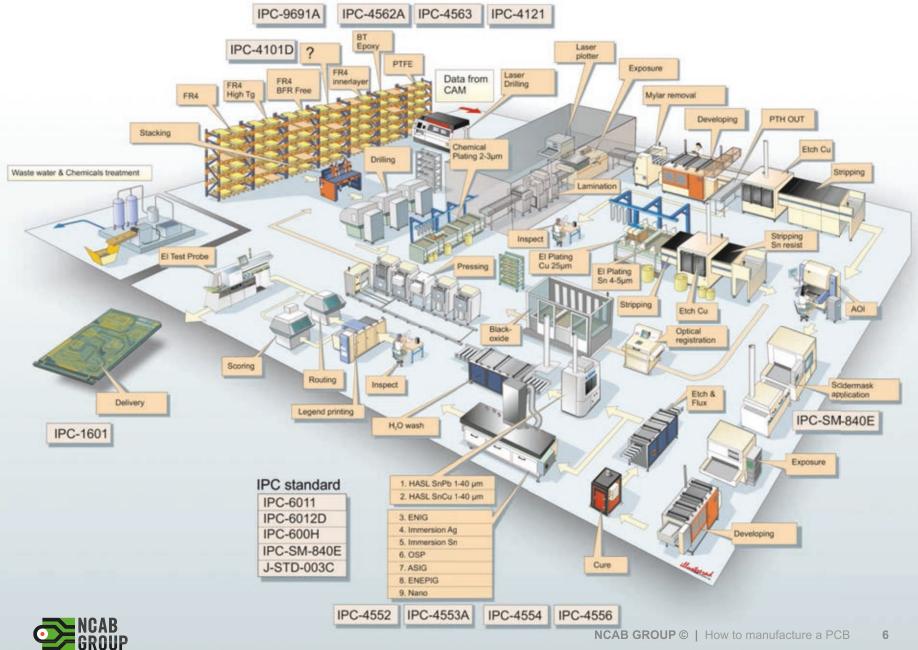

#### **OVERVIEW – MULTILAYER PCB**

### **Overview – Multilayer PCB**

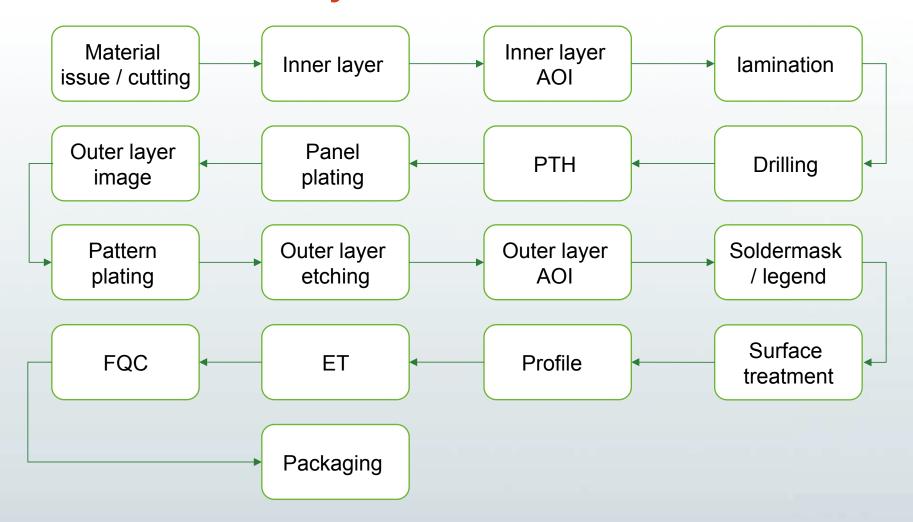

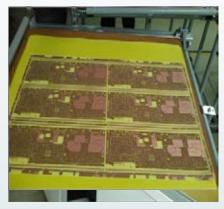

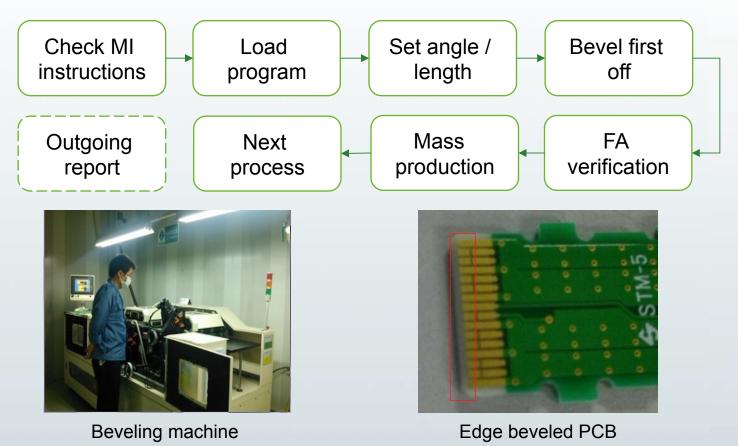

#### MANUFACTURING PROCESS Material issue / cutting

Base material is cut from sheets / larger sizes to working panel sizes.

Sheet cutter – following sizes in manufacturing instruction

Edge beveling machine – to make the corners round

Stage 1 is to transfer the image from an artwork film (based on gerber) to the board surface using photosensitive dry-film and UV light .

**Pre-Treatment**

To clean and oxidize the board surface to increase bond strength between boards and dry film.

Inner layer coating

Photosensitive medium / film is applied to both sides of the material / panel.

#### Automatic exposure

Transferring the image from the artwork to the panel using UV light to polymerise / cross link the areas exposed to UV light.

Stage 2 is to remove the unwanted copper from the panel to form circuitry that matches the image.

**Developing + rinsing**

Developed using either a sodium or potassium carbonate solution. Areas of unexposed dry film are removed first.

#### Etching

Uses either ammonia based on cupric chloride based etchants. The exposed and unwanted copper is etched from the PCB leaving the desired circuitry which is still covered by exposed dry film.

#### Stripping

Using a resist stripper which is caustic in nature, the remaining dry film is removed.

Inspection of the circuitry against digital 'images' (based upon output data) to verify that it is free from such defects as shorts, opens, etc.

Scanning

Board is scanned directly after etching and the image is compared against the data to highlight any differences.

#### Verification

Reliant upon the operators to verify and judge if points highlighted by the scanning are acceptable or not.

Short circuits or excess copper may be repaired at this stage.

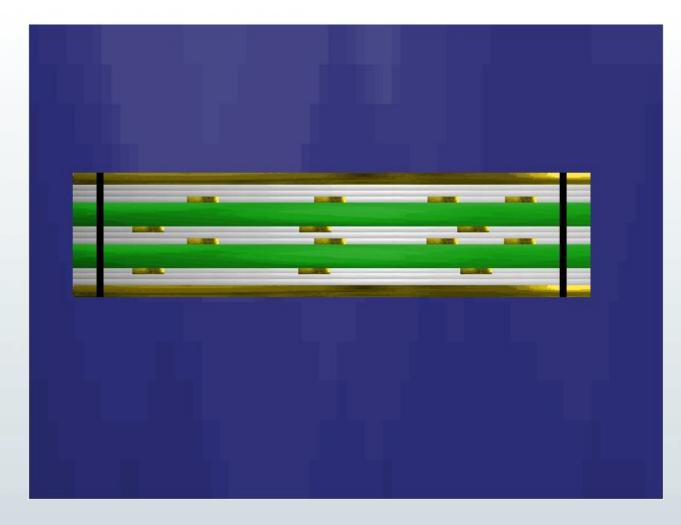

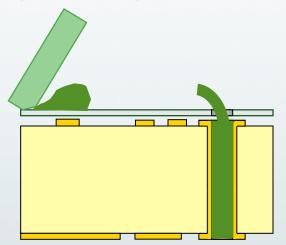

### MANUFACTURING PROCESS Lamination / Bonding

'Fix' the imaged inner layer cores and pre-preg, through bonding them together at a specific temperature and pressure for a specific time to form a solid, multilayer PCB.

# MANUFACTURING PROCESS Lamination / Bonding

# MANUFACTURING PROCESS Lamination / Bonding

Once bonded, the multilayer stack has to be prepared for subsequent processes whilst optimising registration of the inner layer.

X-Ray drilling

Using an x-ray to check the position of targets within each inner layer and then holes are drilled that align all of the targets on the inner layer.

Edge routing

The excess 'flash' material along the edge of each panel from the stack (resin and excess copper foil) is removed.

Edge milling

Similar to the process in the material issue stage, the edges of the panel are prepared through milling to ensure smoothness and prevent handling damage from contact with rough edges.

Inspection

Visual verification that no damage has taken place to the panel during the bonding processes. Earlier within the process the thickness of the bonded panel will be checked against MI data.

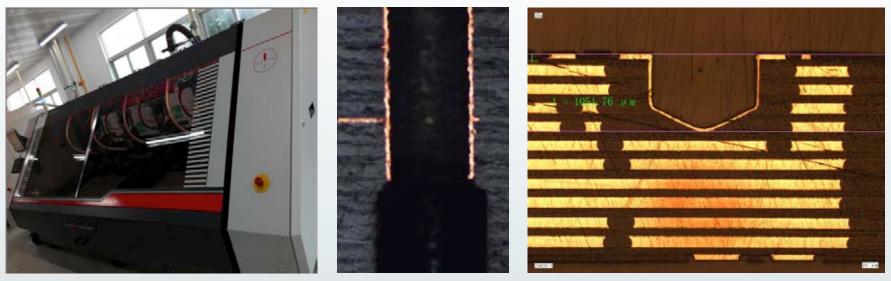

# MANUFACTURING PROCESS Drilling

Drilling of holes to facilitate the provision of electrical continuity between layers.

# MANUFACTURING PROCESS Drilling

Aluminum sheet – entry material

- a. Prevents the drill deflecting to ensure hole accuracy.

- b. Avoid burrs.

- c. Prevents scratches / damage to panel.

#### Base plate – exit material

- a. Prevents drilling through and into the drill machine drill depth should be deeper than board thickness.

- b. Avoid burrs.

- c. Prevents and scratches due to contact with the drill bed.

# MANUFACTURING PROCESS Drilling

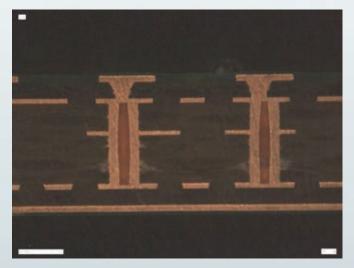

### **Back drilling**

Schmoll drills used.

Special depth tolerance control of ±0.05mm

Panel size limits of 830mm x 1035mm

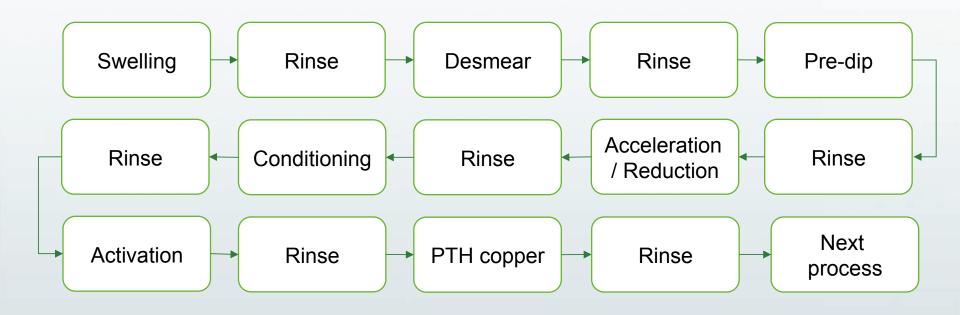

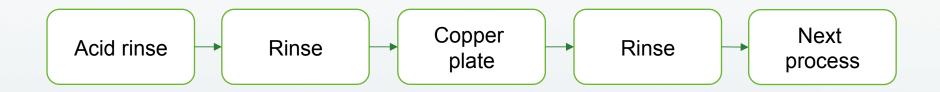

#### MANUFACTURING PROCESS Electroless and Panel plating

Using the two processes the aim is to provide a uniform deposit of copper onto the hole wall through both chemical and electrochemical reactions.

Electroless copper is there only to provide a very thin deposit of  $\leq$  1um that covers the hole wall and also the complete panel.

A complex chemical process that utilises a log of chemistry and with this being the base deposit, if this is poorly controlled then reliability is compromised.

Panel plating follows on from electroless to provide a thicker deposit of copper on top of the electroless deposit – typically 5 to 8 um.

The combination is used to optimise the amount of copper that is to be plated and etched in order to achieve the track and gap demands.

### MANUFACTURING PROCESS Electroless and Panel plating

### **Electroless process**

### MANUFACTURING PROCESS Electroless and Panel plating

### Panel plating process

Board after PTH

Panel plating

Post-processing

### MANUFACTURING PROCESS Outer layer

Similar to the 2 stage inner layer process (image transfer and develop), but with one main difference - we want to remove the dry film where we want to keep the copper / define circuitry.

#### **Pre-Treatment**

To clean and oxidize the board surface to increase bond strength between boards and dry film.

#### **Dry film lamination**

Photosensitive dry film is applied to both sides of the material / panel.

#### Automatic / LDI exposure

Transferring the image from the artwork / data to the panel using UV light / laser to polymerise / cross link the areas exposed.

### MANUFACTURING PROCESS Outer layer

Stage 2, developing, is to remove the unwanted resist from the panel to form circuitry that matches the image.

Developing, rinsing + stripping

#### MANUFACTURING PROCESS Overview – Multilayer PCB

Dry film transitions – from application to imaging to developing.

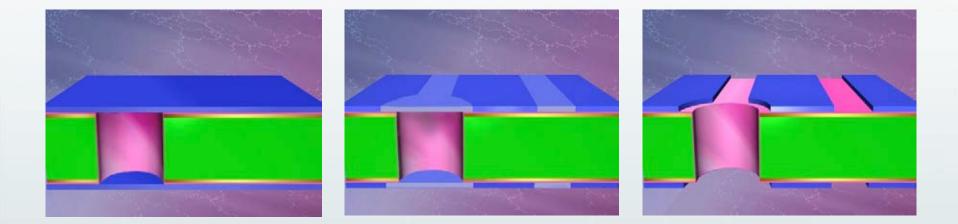

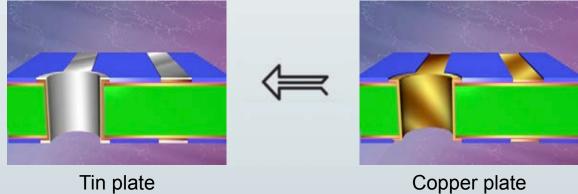

### MANUFACTURING PROCESS Pattern plating

Second electrolytic plating stage, where additional plating is deposited in areas exposed following the imaging process. Takes the plating thickness up to customer demands including NCAB demands of 20um min, 25um average through the hole.

Once the copper has been plated then a deposit of tin is applied to protect the plated copper (underneath the tin), when it is etched away in a subsequent etch process. Once the unwanted copper has been removed, the tin deposit is also chemically removed.

# MANUFACTURING PROCESS Pattern plating

#### Pattern plating process

### MANUFACTURING PROCESS Strip – Etch – De-tin

Removal of the remaining dry film, etching of the unwanted copper and tin thus leaving the copper needed to define the circuitry.

Stripping

Using sodium hydroxide (NaOH) the dry film is removed from the surface.

Etch

Uses either ammonia based on cupric chloride based etchants to removed the unwanted copper under he recently removed dry film.

De-Tin

The tin is removed using nitric acid (HNO3) to leave the copper circuitry.

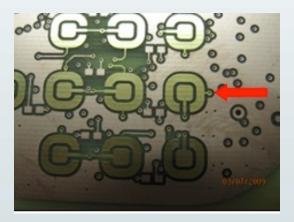

### MANUFACTURING PROCESS Outer layer AOI

Inspection of the circuitry against digital 'images' (based upon output data) to verify that it is free from such defects as shorts, opens, etc.

Scanning

Board is scanned directly after etching and the image is compared against the data to highlight any differences.

#### Verification

Reliant upon the operators to verify and judge if points highlighted by the scanning are acceptable or not.

Short circuits or excess copper may be repaired at this stage.

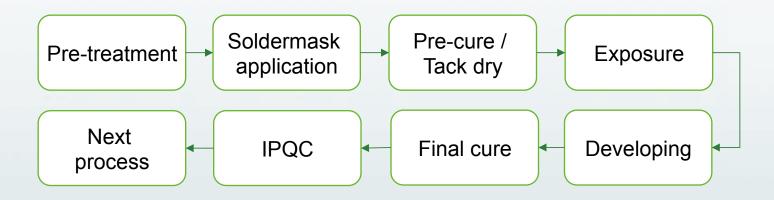

# MANUFACTURING PROCESS Soldermask

The process of applying soldermask ink and generating the soldermask pattern.

# MANUFACTURING PROCESS Soldermask

**Pre-Treatment**

To clean and oxidize the board surface to increase bond strength between boards and dry film.

Soldermask

Using either screen printing (STD) using semi-auto printing machines, or through electrostatic spray coating, soldermask is applied to both sides of the board.

Exposure

Transferring the image from the artwork to the panel using UV light to cross link the areas exposed to UV light – areas we wish to remove are not exposed.

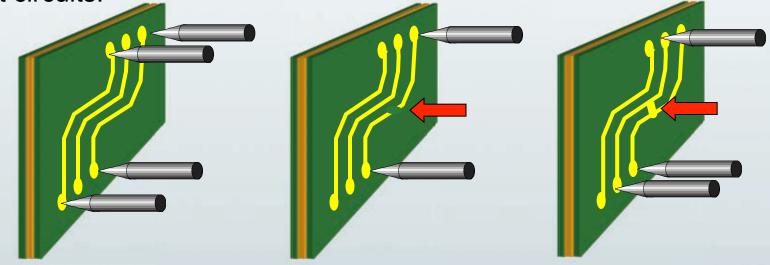

### MANUFACTURING PROCESS Via plugging – soldermask

Using soldermask ink and screen printing to push ink into holes – a separate operation using an aluminium stencil and slightly different squeegee settings.

Critical squeegee differences are (i) angle of blade, (ii) print speed and (iii) pressure. Unlike the normal soldermask process we are trying to push ink **through** the board.

### MANUFACTURING PROCESS Via plugging – soldermask

NCAB Group General PCB requirements:

**General** - When the procurement documentation calls for plugging but doesn't specify which method should be used, then hole plugging shall be as per IPC-4761 Type VI (filled and covered) and shall always take place <u>before</u> soldermask and surface finish.

Plug Depth / Via Hole Fill - Considering boards of 1.60mm, with via hole ranging from 0.25mm – 0.50mm, the target for via hole plugging in accordance with Type VI is 100% fill, but it is considered acceptable if >70% is achieved.

70%

### MANUFACTURING PROCESS Via plugging – resin

Using resin means that there can be completely flat finish to the via holes as the resin sees no shrinkage that can be seen with soldermask as the solvents escape from the ink. A vacuum plugging machine is necessary to achieve the fill.

Typically used for IPC-4761 Type VII via holes – through hole or buried. Copper and silver conductive pastes can also be used

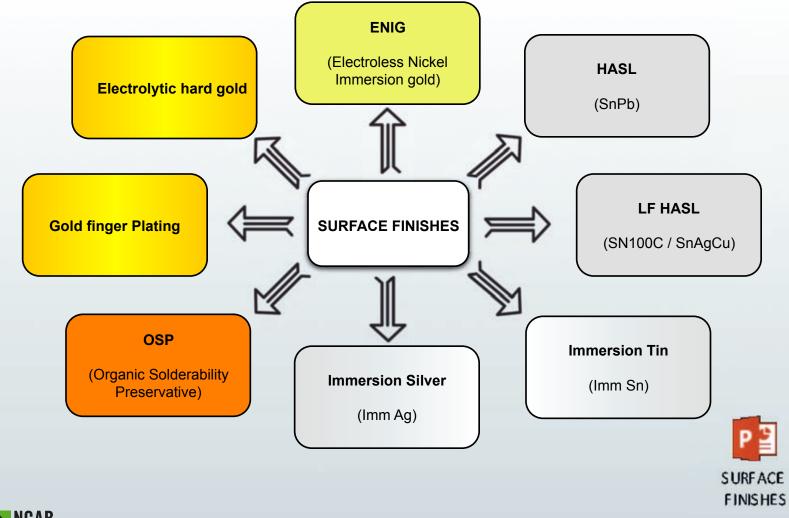

# MANUFACTURING PROCESS Surface finishes

#### ENIG – Immersion gold / Electroless Nickel Immersion Gold

Typical thickness 3 - 6um Nickel / 0.05 - 0.125um Gold. Shelf life: 12 months

- 1. Immersion finish = excellent flatness

- 2. Good for fine pitch / BGA / smaller components

- 3. Tried and tested process

- 4. Wire bondable

- 1. Expensive finish

- 2. Black pad concerns on BGA

- 3. Can be aggressive to soldermask larger soldermask dam preferred

- 4. Avoid soldermask defined BGA's

- 5. Should not plug holes on one side only

Pretreatment

Immersion Gold

Post -treatment

### MANUFACTURING PROCESS ENIG – critical aspects

Critical to quality checking points:

- 1. A complex chemical process with many elements that need to be controlled this is a controlled corrosive process in places.

- 2. Chemistry <u>must</u> be controlled at appropriate frequency ranging from auto monitoring to every six hours / every shift / every day.

- 3. Focus points should include, but not be limited to:

- i. Palladium activator

- ii. Phosphorous content in the nickel bath (note inverse link to pH of nickel bath)

- iii. Nickel content, pH (important for making Ni corrosion resistant) and solution temperature.

- iv. Gold content, pH and solution temperature.

- v. Rinsing quality including sulphuric acid rinse.

- vi. Check for copper content in key baths.

### HASL

#### HASL – Tin/Lead hot air solder level

Typical thickness 1 - 40um. Shelf life:12 months

- 1. Excellent solderability

- 2. Inexpensive / Low cost

- 3. Allows large processing window

- 4. Long industry experience / well known finish

- 5. Multiple thermal excursions

- 1. Difference in thickness / topography between large and small pads

- 2. Not suited for < 20mil pitch SMD & BGA

- 3. Bridging on fine pitch

- 4. Not ideal for HDI products

Pretreatment

HASL

Post-treatment

LF HASL

#### LF HASL – Lead Free hot air solder level

Typical thickness 1 - 40um. Shelf life: 12 months

- 1. Excellent solderability

- 2. Relatively inexpensive

- 3. Allows large processing window

- 4. Multiple thermal excursions

- 1. Difference in thickness / topography between large and small pads but to a lesser degree than SnPb

- 2. High processing temperature 260-270 degrees C

- 3. Not suited for < 20mil pitch SMD & BGA

- 4. Bridging on fine pitch

- 5. Not ideal for HDI products

Pretreatment

HASL

Post-treatment

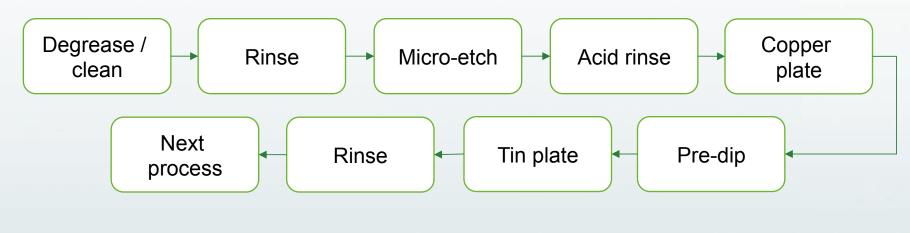

### **Immersion tin**

#### Immersion Sn – Immersion Tin

Typical thickness ≥ 1.0µm. Shelf life: 6 months

- 1. Immersion finish = excellent flatness

- 2. Good for fine pitch / BGA / smaller components

- 3. Mid range cost for lead free finish

- 4. Press fit suitable finish

- 5. Good solderability after multiple thermal excursions

- 1. Very sensitive to handling gloves must be used

- 2. Tin whisker concerns

- 3. Aggressive to soldermask soldermask dam shall be ≥ 5 mil

- 4. Baking prior to use can have a negative effect

- 5. Not recommended to use peelable masks

- 6. Should not plug holes on one side only NOTE: contains Thiourea (cariogenic in nature)

Pretreatment

Immersion Tin

Post -treatment

### **Immersion silver**

#### Immersion Ag – Immersion Silver

Typical thickness 0.12 - 0.40um. Shelf life: 6 months

- 1. Immersion finish = excellent flatness

- 2. Good for fine pitch / BGA / smaller components

- 3. Mid range cost for lead free finish

4. Can be reworked NOTE: suitable for wire bonding

- 1. Very sensitive to handling / tarnishing / cosmetic concerns gloves must be used

- 2. Special packaging required if packaged opened and not all boards used, it must be resealed quickly.

- 3. Short operating window between assembly stages

- 4. Not recommended to use peelable masks

- 5. Should not plug holes from one side only

- 6. Reduced supply chain options to support this finish

Immersion Ag

### OSP

#### OSP (Organic Solderability Preservative)

Typical thickness 0.20-0.65µm. Shelf life: 6 months Suntak thickness is 0.3 - 0.5um

- 1. Excellent flatness

- 2. Good for fine pitch / BGA / smaller components

- 3. Inexpensive / Low cost

- 4. Can be reworked

- 5. Clean, environmentally friendly process

- 2. Short operating window between assembly stages

- 3. Limited thermal cycles so not preferred for multiple soldering processes (>2/3)

- 4. Limited shelf life not ideal for specific freight modes and long stock holding

- 5. Very difficult to inspect

- 6. Cleaning misprinted solderpaste can have a negative effect on the OSP coating

- 7. Baking prior to use can have a negative effect

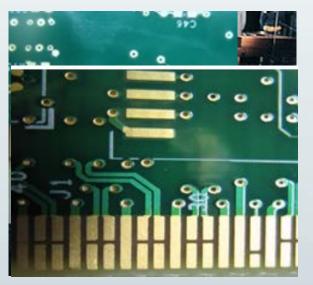

#### MANUFACTURING PROCESS Hard gold contacts and gold fingers

Electrolytic nickel gold Typically - internal hard gold contacts. Plated using 'normal' electrolytic process so current is necessary - features must be tracked out to the edge of the panel for continuity.

Edge contacts or gold fingers. Again using nickel and gold deposits.

Uses a conveyorised plating series of baths with limited depth. Areas exposed (not taped up) will be plated with gold.

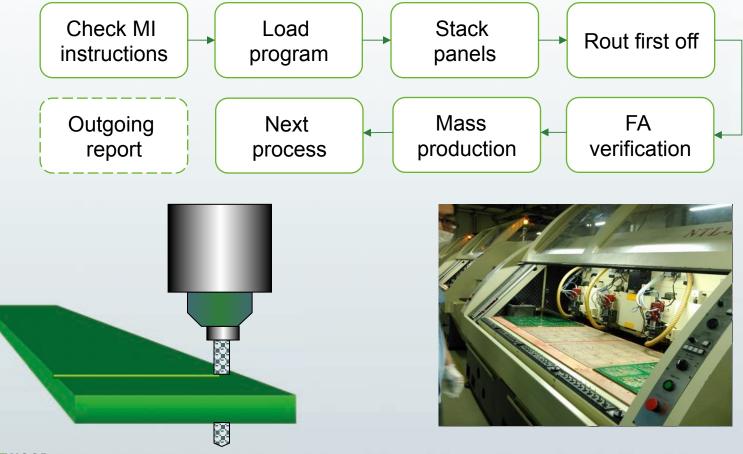

## MANUFACTURING PROCESS <br/> Profile

Routing – cutting the circuits to specific shape and size.

## MANUFACTURING PROCESS <br/> Profile

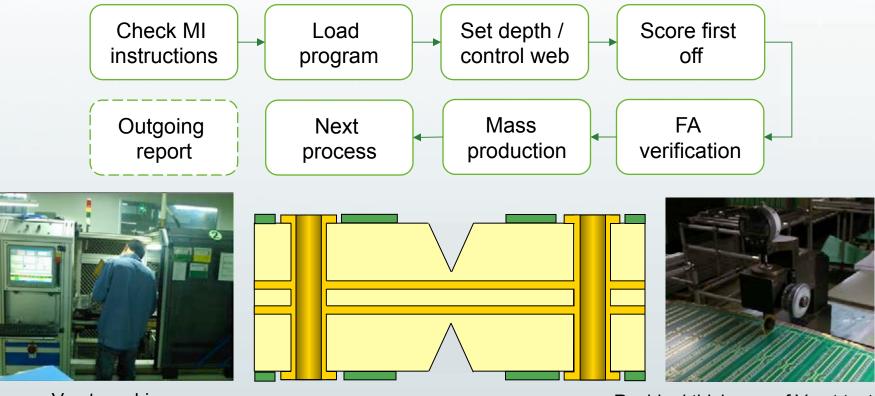

Scoring / V-cut – Cutting a groove into the panel for ease of depaneling.

V-cut machine

Residual thickness of V-cut test

## MANUFACTURING PROCESS <br/> Profile

Edge beveling – typically on edge fingers for ease of insertion.

### MANUFACTURING PROCESS Electrical test

Used for checking the integrity of the tracks and the through hole interconnections – continuity and isolation where needed.

Continuity means testing the resistance on the same net – check for open circuits.

Isolation means testing the resistance between different nets – check for short circuits.

### MANUFACTURING PROCESS Electrical test

All machines should be set up using IPC-9252 class 2, as the benchmark for test voltage, isolation and continuity resistance. Bed of nails (2 fixtures testing top and bottom of PCB simultaneously) is standard for volume production.

Automatic segregation test machine using 'bed of nails' - LMHV

## MANUFACTURING PROCESS Electrical test

All machines should be set up using IPC-9252 class 2, as the benchmark for test voltage, isolation and continuity resistance.

Flying probe test machines - HMLV

Checking the PCB for acceptance criteria as defined in customer specifications / NCAB general demands / IPC-A-600. Can be carried out thought manual visual inspection and more recently with the aid of AVI (compares PCB to gerber) – but this still relies on inspectors to make judgements as to acceptance and also if boards that deviate, can be repaired or scrapped.

AVI can see defects as small as 35um and has a faster checking speed that human eyes. Can cover almost all aspects of acceptance.

Automated Visual Inspection - AVI

# MANUFACTURING PROCESS Testing

SEM & EDS

Atomic Adsorption Spectrometer

Ion Chromatograhy Analyze Machine

SIR test system

Impedance Tester

XRF RoHS Tester

TG Tester

XRF thickness checker

Thermal Shock Machine

Reflow Oven

Salt Spray tester

Hot oil tester Machine

# **Factory Differences**

So now we understand how a PCB is made. But how are the factories set up?

Are they all the same?

Do we need different factories for different PCB's?

Different technologies will not all be covered in one single factory, quite often they will specialise in certain technologies:

- Single sided

- Double sided

- Multilayer

- Flex / Flex-rigid

- HDI

- IMS

- Military / Automotive / Medical / Aerospace (high demands)

Different technologies will often necessitate different standards of equipment – for example a basic single sided factory may not have the necessary equipment to manufacture reliable higher layer count products.

As with different technologies, different volumes and lead times will necessitate different factories who can cope with such different demands:

- Prototypes

- Medium volumes

- High volumes

- Fast turnaround

- Asia vs. Europe

In summary; it is very important to select the right combination of factory setup and match that to the type of the PCB, and also the demand.

Get this wrong and results could include:

- The lead times quoted might not match the actual delivery.

- The quantity delivered might not be full quantity.

- The factory may not truly have the technical competence to reliably make the board and this might not be apparent upon receipt!

- The cost may be unnecessary high.

# Questions?

RoHS

位工作力推要 長輩安全指訴的

### NCAB GROUP SEMINARS Improve your knowledge about PCBs – participate in our seminars

Technical trends in the global PCB industry How to produce a printed circuit boards New technologies Cost drivers in PCB production Surface finishes HDI - High Density Interconnect IMS - Insulated Metal Substrate Rigid-flex NCAB Group PCB Specification

Impedance controlled boards

DFM – Design For Manufacturing

IPC vs. Perfag

Reliability, IPC & NCAB

Material for lead-free production

Technical advice

NCAB Group Laboratory