Dans la production de circuits imprimés, le temps, c’est de l’argent, mais pas toujours comme les ingénieurs l’imaginent. Une conception de circuit haute performance négligeant la fabricabilité peut entraîner l’arrêt complet du lancement d’un produit. De plus, les conséquences les plus coûteuses d’un DfM défaillant se cachent souvent dans les coûts indirects : temps passé en retouches, échanges avec les fournisseurs, échecs de tests et retards imprévus.

Comment minimiser les coûts indirects, raccourcir les délais et maintenir votre conception sur la bonne voie

Cet article met en évidence comment les pièges courants d’un DfM augmentent les délais de production et les coûts non matériels, et présente des stratégies pratiques pour aider les équipes de conception et de fabrication à collaborer plus efficacement.

Coûts indirects : les « tueurs » de budget cachés

Lorsqu’une production stagne, il s’agit rarement d’un simple problème matériel. Les coûts (dépenses indirectes, souvent non comptabilisées) peuvent augmenter considérablement le coût total d’une carte. Parmi ceux-ci, on peut citer :

- Temps d’ingénierie supplémentaire pour corriger les déviations DfM

- Échanges avec les fabricants concernant des données ambiguës

- Retards d’assurance qualité dus à une mauvaise testabilité

- Retards d’approvisionnement dus à des composants non standard

- Reprise de l’assemblage suite à des problèmes de configuration

Ces problèmes n’affectent pas seulement la fabrication en cours. Ils se répercutent sur les cycles de production en aval, les réclamations sous garantie et même l’atteinte à la réputation. Et surtout, ils retardent la mise sur le marché, là où le véritable coût se fait sentir.

Piège n°1 : Sur-spécifications et tolérances serrées

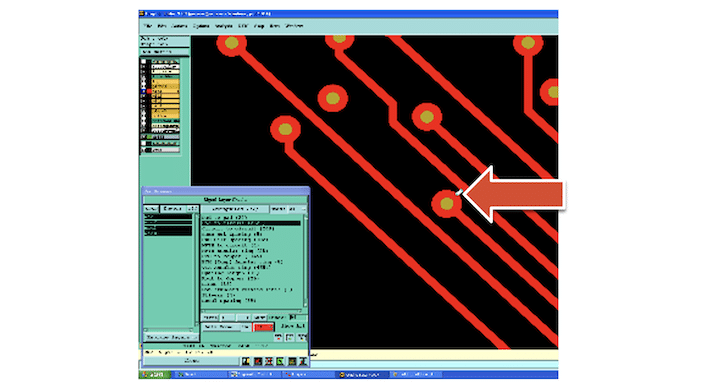

Spécifier des largeurs de pistes, des isolements ou des tailles de vias ultra-serrés, au-delà des capabilités standard d’un fabricant, augmente non seulement les coûts, mais aussi les délais.

Pourquoi est-ce problématique :

- Nécessite un outillage et un contrôle de process avancés

- Entraîne des retards FAO lors de la revue de conception

- Peut déclencher des demandes de modifications techniques (DMO)

Mesures d’atténuation :

Concevez toujours dans les limites des directives DfM standard de votre usine, sauf nécessité absolue. Des tolérances plus strictes doivent répondre à des besoins de performance, et non à une perfection théorique.

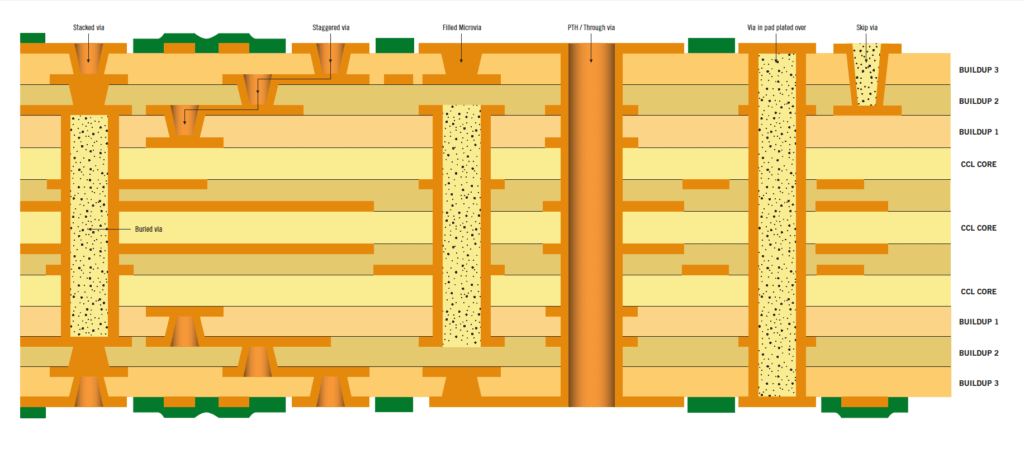

Piège n° 2 : Empilements complexes et microvias sans planification

Les circuits imprimés multicouches et les conceptions HDI sont courants dans les applications haute densité actuelles. Cependant, spécifier des vias borgnes/enterrés ou des matières non standard sans vérifier la disponibilité et les délais peut bloquer la production.

Incidence des coûts :

- Nécessite des cycles de lamination spécialisés.

- Réduit la flexibilité du fournisseur.

- Augmente le risque de rebut dû à un mauvais alignement des couches.

Mesures d’atténuation :

Coordonnez-vous avec votre fabricant en amont pour vérifier l’empilement de vos couches. Utilisez des calculateurs à impédance contrôlée et vérifiez la disponibilité des matières pendant la mise en œuvre, et non après.

Piège n° 3 : Documentation de fabrication incomplète ou peu claire

Les fichiers Gerber, les fichiers Pick-and-Place et les tableaux de perçage contenant des informations manquantes ou contradictoires sont source de retards.

Conséquences concrètes :

- Les fabricants suspendent la fabrication en attendant des clarifications.

- La résolution des problèmes ajoute 2 à 4 jours à la production.

- Peut entraîner la fabrication de cartes selon des spécifications incorrectes.

Mesures d’atténuation :

Vérifiez tous les résultats de fabrication.

Inclure :

- Des noms de nets et des diamètres de perçage clairs.

- Des diagrammes d’empilement avec les matériaux et les épaisseurs.

- Le marquage des fonctions des couches prévues (par exemple, signal, alimentation, masse).

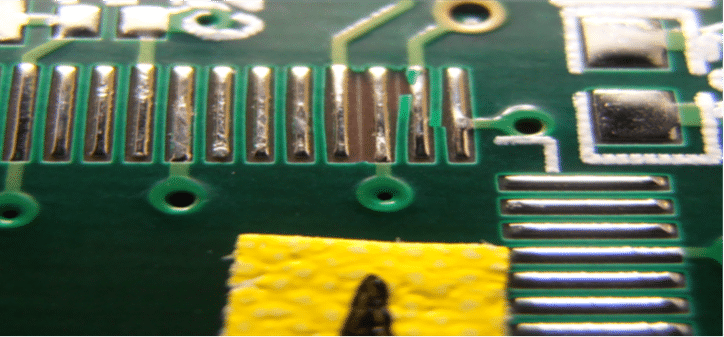

Piège n° 4 : Mauvais placement et mauvaise orientation des composants

Les circuits imprimés denses, dont les composants sont placés pour des raisons pratiques (et non pour l’assemblage), sont un oubli fréquent des DfM. Cela inclut des pièces polarisées mal alignées, des pastilles de tailles irrégulières et des tolérances minimes.

Impact sur les coûts :

- Vitesses de placement plus lentes ou placements rejetés.

- Risque accru de composant se soulevant ou de pontage.

- Inspection ou reprise manuelle.

Mesures d’atténuation :

Alignez les composants polarisés de manière cohérente. Laissez un espace suffisant autour des BGA ou des composants hauts. Consultez la norme IPC-7351 et les exigences de votre assembleur en matière de repères lors de l’implantation.

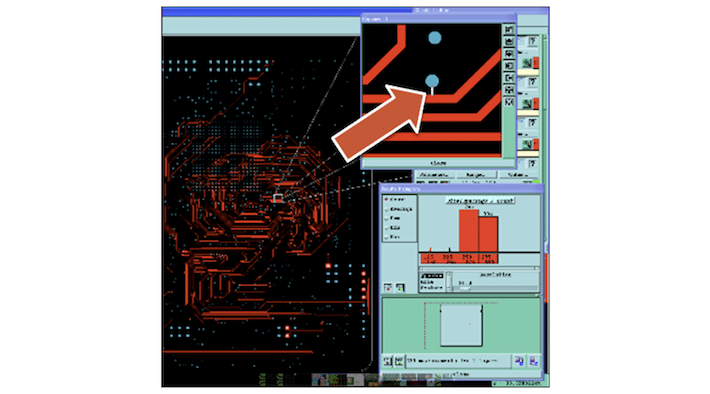

Piège n° 5 : Ignorer la testabilité (DFT)

L’absence de conception adaptée aux tests entraîne un nombre accru de pannes sur le terrain et des cycles de débogage plus longs.

Coûts indirects cachés :

- Augmentation des coûts de maintenance sur le terrain due à des problèmes difficiles à diagnostiquer.

- Retards lors des tests et de la validation fonctionnels.

- Difficultés d’accès aux nœuds pour les technologies de l’information et de la communication (TIC) ou le JTAG.

Mesures d’atténuation :

Ajouter des points de test pour les signaux clés. S’assurer qu’aucun composant ne bloque l’accès aux sondes. Inclure une chaîne de balayage des limites si possible. Documenter clairement les attentes en matière de couverture des tests pour votre assembleur.

Piège n° 6 : Utiliser des composants obsolètes ou difficiles à trouver

La pièce peut fonctionner sur papier, mais si elle est obsolète ou si son délai de livraison est de 52 semaines, la production est bloquée.

Risques liés à la chaîne d’approvisionnement :

- Reconceptions involontaires de dernière minute.

- Le re-sourcing augmente les risques et les incohérences.

- Augmentation du coût global du produit en raison de l’expédition

Mesures d’atténuation :

Impliquer les équipes d’approvisionnement ou les partenaires EMS lors de la création des schémas. Utiliser des pièces AVL (liste des fournisseurs approuvés) lorsque cela est possible et valider l’état du cycle de vie (via Octopart, Silicon Expert, etc.) avant la publication de la nomenclature finale.

Piège n° 7 : Ne pas tenir compte de l’impact des décisions de fabrication sur les délais de livraison

Le DfM ne se limite pas à la faisabilité de la fabrication, mais aussi à sa rapidité. Concevoir aux limites de la fabricabilité ralentit chaque étape.

Amplificateurs de délais :

- Remontées de l’équipe FAO pour les conceptions hors spécifications.

- Inspections AQ supplémentaires.

- Retards d’approvisionnement en matières (par exemple, substrats non standard).

Mesures d’atténuation :

Demandez-vous toujours « Combien de temps cela prendra-t-il pour la fabrication ?» lorsque vous finalisez chaque aspect de la conception : empilement, type de via, finition, épaisseur du cuivre. En cas de doute, contactez votre partenaire de fabrication ou EMS avant la mise en production.

Meilleures pratiques pour réussir en DfM

Les recommandations suivantes rationalisent les coûts de production et les coûts indirects :

| Action | Avantage |

| Implication précoce du fabricant | Réduction des déviations et des modifications DfM |

| Stack-up standard et utilisation via | Minimisation des process spéciaux et des cycles de lamination |

| Packs de données complets | Accélération des devis et suppression des ambiguïtés |

| Contrôles du cycle de vie des composants | Évitement des modifications de conception dues aux pièces en fin de vie/non conformes |

| Analyses DfM dédiées | Détection des erreurs avant la publication et réduction des questions techniques. |

Directives de conception ≠ Menu de conception : comprendre ce qui peut (et ne peut pas) être combiné

En tant qu’ingénieurs concepteurs de circuits imprimés, vous êtes habitués à travailler avec des contraintes strictes. Mais il est important de comprendre qu’une liste de fonctionnalités n’est pas un menu de fonctionnalités interchangeables. Nous voyons souvent des conceptions où les clients pensent pouvoir combiner, par exemple, une protection de via de type VI ou VII avec des géométries de lignes/isolements les plus serrées possibles, pour finalement obtenir une carte qu’aucun fabricant ne peut fabriquer.

Un problème fréquent : un concepteur considère l’espacement minimal pour les trous traversants métallisés et remplit ensuite la carte de manière dense avec des vias, laissant peu ou pas de diélectrique entre eux. Cela rend la lamination physiquement impossible, car il ne reste pas assez de matière pour maintenir les couches ensemble.

Autre cas : un client s’est référé à nos directives UHDI et a disposé des pistes parallèles de 20 µm sur toute la carte pour connecter une puce, en spécifiant du hard gold sur les plots de connexion ultrafins. Même les procédés mSAP les plus avancés ne permettent pas cette combinaison. En réalité, les lignes fines et le hard gold s’excluent souvent mutuellement, en raison des tolérances de métallisation et des dimensions.

En résumé : les limites de capacité ne sont pas cumulatives. Il est essentiel de concevoir dans la fenêtre de process, et non à l’intersection de chaque extrême. Comprendre l’interaction des différents paramètres de conception (mécaniquement, chimiquement et thermiquement) est tout aussi important que connaître leurs limites individuelles. En cas de doute, contactez votre fabricant au plus tôt. Cela vous fera gagner du temps, de l’argent et vous évitera une refonte fastidieuse.

Exemple concret : comment le DfM a réduit les délais d’exécution

Une start-up américaine a conçu une carte haute densité à 10 couches avec des microvias de 0,075 mm et des paires de vias borgnes/enterrés. Le projet a subi un retard de six semaines, le fabricant choisi ne pouvant pas respecter les tolérances. Après consultation de son partenaire EMS et reconception avec des vias empilés standard et des trous de 0,1 mm, la production a repris en moins de 10 jours, avec une réduction des coûts de 15 %.

Réflexions finales

Le DfM n’est pas une simple liste de contrôle, c’est un état d’esprit. Les produits les plus performants en réalisation ne sont pas seulement rapides en conception ; ils sont conçus pour l’être en production.

En réduisant les déviations des normes DfM, en minimisant la complexité et en communiquant clairement avec les partenaires de fabrication, les ingénieurs peuvent respecter les délais, réduire les coûts indirects et accélérer la rentabilité. Sur un marché de l’électronique concurrentiel, une bonne conception DfM n’est plus un avantage, c’est un impératif commercial.

Obtenez votre conception dès le départ grâce à nos règles de conception de circuits imprimés

Les règles de conception pour les circuits imprimés multicouches, HDI, Ultra HDI, Flex/Rigid-Flex, Semi-Flex, Copper Coin, Via Protection, Stackups et Impédances sont disponibles en téléchargement.

Téléchargez nos règles de conception de circuits imprimés ici