Die Definition des richtigen Lagenaufbaus gehört zu den größten Unsicherheiten von Elektronikentwickler. Warum weichen die tatsächlichen Leiterplattendicken nach der Fertigung oft von den geplanten Werten ab? Wie viele Prepreg-Lagen sind nötig, um die gewünschte Isolationsdicke zu erreichen? In diesem White Paper geben wir Ihnen klare Antworten und praxisnahe Tipps, damit Ihre Designs von Anfang an auf Erfolgskurs sind.

Es gibt kein Handbuch, das alle Fragen zum PCB-Stackup Schritt für Schritt beantwortet. Genau deshalb möchten wir in diesem Beitrag etwas Klarheit schaffen.

Wie sieht der typische Workflow für PCB-Designer aus?

- Basismaterial auswählen

- Anzahl der Lagen und Kupferstärken festlegen

- Stackup definieren

Klingt einfach – ist es aber nicht. Denn solange diese Parameter nicht eindeutig definiert und mit dem Hersteller abgestimmt sind, kann kein Designer präzise Leiterbahnen im EDA-Tool setzen, insbesondere gilt dies für impedanzdefinierte Lagenaufbauten. Darüber hinaus ist es entscheidend, die minimalen Kupferdicken für Innen- und Außenlagen gemäß den IPC-Vorgaben (IPC-6012, Tabellen 3-17 und 3-18) zu berücksichtigen. Diese Werte sind nicht nur ein formaler Standard, sondern beeinflussen direkt die Stromtragfähigkeit, die Wärmeabfuhr und damit die Zuverlässigkeit Ihrer Leiterplatte. Unklare Spezifikationen führen oft zu Verzögerungen und unnötigen Anpassungen.

Die richtige Auswahl des Basislaminates

Die Wahl des Isoliermaterials – also des Dielektrikums – richtet sich nach der Anwendung: Für industrielle Schaltungen ohne Hochfrequenzsignale oder hohe Datenraten kommt in der Regel ein Standard-FR4-Laminat mit passendem Prepreg zum Einsatz. Als Faustregel für die Dauerbetriebstemperatur gilt: Bei Materialien bis TG150 wird ein Faktor von 0,80 angesetzt, ab TG170 reduziert sich dieser auf 0,85 z.B.: bei einem TG150 Material x0,8=120C° oder TG170x0,85= 144,5C° Dauerbetriebstemperatur.

Das Standardmaterial besteht aus einem Glasfasergewebe, das mit Epoxidharz getränkt ist. Die Kerne sind beim Laminathersteller bereits ausgehärtet und üblicherweise beidseitig kupferkaschiert. Das Prepreg hingegen wird im nicht ausgehärteten Zustand geliefert und muss in der Leiterplattenfertigung separat klimatisiert gelagert werden.

Im Gegensatz dazu kommen in Telekommunikationsanwendungen, die bei Frequenzen über 5 GHz arbeiten, Hochfrequenz-Laminate mit anderer Glasfaserstruktur und einem speziellem Epoxidharzsystem zum Einsatz – diese können bis zu 15-mal teurer sein als Standard-FR4.

In kommerziellen Anwendungen mit hohen Stückzahlen wird in der Regel FR4-Material verwendet. Hier sind Werte wie die Dielektrizitätskonstante (Dk) oder der Verlustfaktor (Df) weniger kritisch als bei RF- oder High-Speed-Daten-Anwendungen.

Glasfasergewebe: Unsichtbarer Einfluss auf Ihr Design

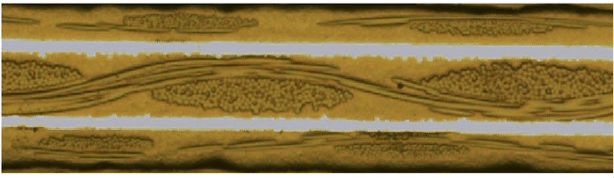

Die Glasfaserstruktur des FR4-Materials beeinflusst nicht nur die mechanische Stabilität, sondern auch die elektrischen Eigenschaften Ihrer Leiterplatte. FR4-Materialien werden mit unterschiedlichen Glasfasergewebe-Strukturen hergestellt. Diese Gewebe verleihen der Harzbasis Flexibilität und ermöglichen die Anpassung der Materialdicke. Das Beispiel im unten gezeigten Bild zeigt die verflochtenen Fasern eines 2113-Kerns (in der Mitte), seine beiden Kupferfolien (grau) sowie zwei Lagen 106-Prepreg darüber und darunter. Man erkennt deutlich, dass die Dickenunterschiede hauptsächlich durch die Verwendung unterschiedlicher Fasergrößen erreicht werden.

FR4 Materialien haben sich über die Jahre erheblich weiterentwickelt und bieten heute eine deutlich verbesserte thermische, elektrische und mechanische Performance. Dazu zählen unter anderem: geringere Ausdehnungskoeffizienten (CTE) in der Z-Achse, niedrigere CTE-Werte in X-Y-Richtung, höhere Rissbeständigkeit sowie eine breite Auswahl an Harzsystemen, die mit anderen Materialien nicht realisierbar wären. Diese Eigenschaften – kombiniert mit ihrer Wirtschaftlichkeit – machen sie zu den am häufigsten eingesetzten Basismaterialien in der Leiterplattenindustrie.

Im Bereich hoher Frequenzen und High-Speed-Anwendungen stoßen Standard-FR4-Materialien jedoch an ihre Grenzen:

- Dielektrizitätskonstanten (Dk) müssen über einen breiten Frequenz- und Temperaturbereich stabil bleiben. Niedrige Dk-Werte sind bevorzugt, um Signallaufzeiten zu reduzieren und eine hohe Signalintegrität sicherzustellen.

- Geringe dielektrische Verluste (niedriger Df) sind erforderlich, um Signalenergieverluste zu minimieren.

- Zudem steigen die thermischen Anforderungen an das Substrat erheblich – insbesondere bei steigender Frequenz, da die Temperaturbelastung in solchen PCBs extrem zunimmt.

Im Gegensatz zu Standard-FR4, dessen Fertigungsprozesse stark standardisiert sind und hohe Ausbeuten zu wettbewerbsfähigen Preisen ermöglichen, gilt für einige Hochfrequenz-Laminate das Gegenteil:

PTFE (Teflon)-Laminate bieten exzellente elektrische Eigenschaften, erfordern jedoch spezielle Fertigungsprozesse, die oft außerhalb der Standardverfahren liegen. Das macht sie deutlich teurer und kann die Herstellung sogar unpraktikabel machen, wenn diese Prozesse stark von den FR4-Methoden abweichen. Hier hängt vieles von den technischen Möglichkeiten des Herstellers ab.

Um diese Herausforderungen zu meistern, wurden Materialien entwickelt, die optimale elektrische Eigenschaften bieten und gleichzeitig mit Verfahren ähnlich denen von FR4 verarbeitet werden können. Dazu gehören keramikgefüllte PTFE-Laminate und duroplastische Kohlenwasserstoff-Laminate. Beide behalten hervorragende elektrische Eigenschaften bei und stellen weniger Hürden in der Fertigung dar.

Ein Beispiel aus der Praxis: Der Bohrprozess. PTFE-Materialien erfordern andere Bohrparameter (Drehzahl, Vorschub etc.). Hinzu kommt die Reinigung der Bohrlöcher (Desmearing), die im Gegensatz zu Standardmaterialien besondere Aufmerksamkeit vom Leiterplattenhersteller verlangt.

Die Lagenanzahl und dessen Kupferstärken

Bei der Definition des Lagenaufbaus müssen zahlreiche Faktoren berücksichtigt werden. Ähnlich wie im Bauwesen gilt: Wenn die verfügbare Fläche begrenzt ist, baut man in die Höhe. Bei Leiterplatten nähert sich die nutzbare Fläche in der Regel der Fläche, die durch die Bauteil-Footprints und Gehäusevorgaben bestimmt wird. In manchen Fällen stoßen wir sogar an diese Grenze: Der Standard IPC-7092 beschreibt die Prozesse, die erforderlich sind, um aktive und passive Komponenten direkt im Substrat einzubetten. Wir konzentrieren uns hier jedoch auf Standardtechnologien der Leiterplattenfertigung, da Embedded-Technologien vor allem für mobile Elektronik im Consumer-Bereich relevant sind – was sich auch darin zeigt, dass weltweit nur eine Handvoll Hersteller diese Verfahren anbietet.

Diskrete Bauteile werden weiterhin optimiert: BGA-Packages erreichen inzwischen Pitch-Werte unter 0,4 mm. Das Routen einer so hohen Pin-Dichte pro Quadratzentimeter erfordert eine große Anzahl an Lagen. Und sobald der Pitch 0,35 mm oder kleiner wird, sind sogar neue Fertigungstechnologien wie mSAP notwendig.

Impedanzdefinierte Leitergeometrien und Wärmeentwicklung

Ein weiterer entscheidender Faktor für die Anzahl der PCB-Lagen ist die Frage, ob kontrollierte Impedanzleitungen erforderlich sind. Solche Leitungen benötigen Referenzebenen – entweder unterhalb (Microstrip-Topologie) oder ober- und unterhalb der Impedanzleitungen (Stripline-Topologie) – und erhöhen dadurch die Anzahl der Lagen. Außerdem bestimmen diese Leitungen die Dicke der Isolationsschichten, da Impedanz und Prepreg-Dicke direkt miteinander verknüpft sind.

Ein zusätzlicher Einflussfaktor auf die PCB-Topologie ist die Wärmeentwicklung: Kupfer ist kein perfekter elektrischer Leiter und erzeugt Verluste in Form von Wärme, die abgeführt werden muss. Die unterschiedlichen Ströme in den Power-Netzen bestimmen die Dicke der Stromversorgungsebenen. In solchen Fällen legt der PCB-Designer die Kupferdicke fest – aus der großen Auswahl an verfügbaren Kupfergewichten.

Um die Leiterplatte vor übermäßiger Erwärmung zu schützen, ist es entscheidend sicherzustellen, dass die Temperaturerhöhung unter normalen Betriebsbedingungen eine Sicherheitsmarge unterhalb der Glasübergangstemperatur (Tg) des Materials nicht überschreitet. Hierfür greifen wir auf die Diagramme der IPC-2152 zurück.

Finalisierung des Lagenaufbaus

Sobald die Auswahl und die Anzahl der Lagen mit deren Kupferstärken festgelegt sind, muss die gesamte Soll-Dicke angepasst werden. Obwohl 1,6 mm die gängigste Dicke ist, kann bei Bedarf jede andere Stärke spezifiziert werden.

Das übliche Fertigungsverfahren basiert darauf, laminierte Kerne abwechselnd mit Prepreg-Lagen zu stapeln (das Prepreg liefert gleichzeitig das Harz, das zum Verkleben und Laminieren des Aufbaues benötigt wird). Der Stapel wird außen mit zwei Kupferfolien abgeschlossen, die mithilfe von Prepreg angebracht werden. Diese Reihenfolge des Stapelns bezeichnet man als Stackup.

Als Designregel gilt: Bei einer konventionellen Leiterplatte (nicht HDI) bestehen die beiden äußeren Isolationslagen immer aus Prepregs, da sie als Träger für die obere und untere Kupferfolie dienen. Die übrigen Innenlagen bestehen aus laminierten Kernen, die ebenfalls mit Prepregs verbunden werden. Das Ergebnis ist eine Struktur, die in der Regel eine gerade Anzahl an Lagen aufweist.

Alle wichtigen Stackup-Tipps und Impedanzdefinition

Maximal drei Prepreg-Lagen

Prepreg-Lagen können kombiniert werden, um die gewünschte Isolationsdicke zwischen den Kupferlagen zu erreichen – jedoch sollten pro Ebene nicht mehr als drei Prepregs eingesetzt werden. Ist die erforderliche Dicke zwischen zwei Kupferschichten so groß, dass sie mit drei Prepregs nicht erreicht werden kann, wird ein zusätzlicher kupferfreier Laminatkern verwendet. Solche kupferfreien Laminate sind verfügbar, oder einige Hersteller entfernen eine oder beide Kupferkaschierungen des Kerns durch Ätzen.

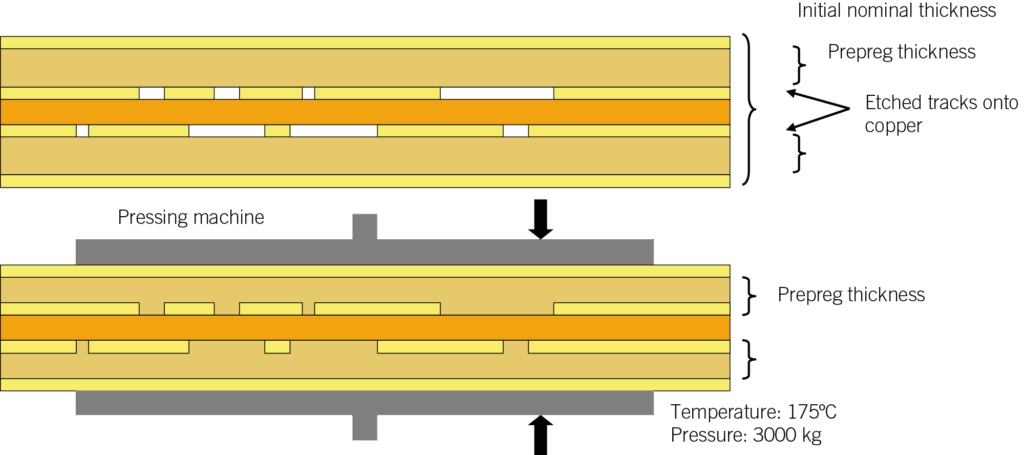

Der korrekt gestapelte und ausgerichtete Aufbau wird in eine vakuumunterstützte, heiße Hydraulikpresse gelegt – bei etwa 175 °C (rund 30 °C über der Glasübergangstemperatur des Materials) und einem Druck von ca. 3000 kg/m² für etwa zwei Stunden, bis der Aufbau vollständig ausgehärtet ist. Anschließend erfolgt eine kontrollierte Abkühlung in der Kaltverpressung, um Verwindung und/oder Verwölbung des Aufbaus zu vermeiden.

Während des Heißverpressens tritt die Dickenreduzierung des Prepregs auf – oft zur Überraschung der Designer: Das Harz fließt in die „Hohlräume“, die in kupferfreien Bereichen nach dem Ätzen entstanden sind. Diese Reduktion wird bei der Planung der nominalen Lagenstärke meist nicht berücksichtigt und führt so gut wie immer zu technischen Rückfragen.

Ein interessanter Effekt dieser Prepreg-Dickenreduzierung ist, dass die charakteristische Impedanz der Signalleitungen abnimmt, da die Referenzlagen nun näher an den Impedanzdefinierten Leiterbahnen liegen.

Diese Berechnungen werden bei der Aufbereitung der PCB-Daten bei uns angepasst und mit dem Entwickler über die technische Klärung freigegeben. Dafür werden die Datenblätter der Prepreg- und Kerne benötigt sowie Details zum geätzten Layout, und insbesondere die jeweiligen Erfahrungswerte der Leiterplattenfabrik:

- Die nominalen Kupferdicken

- Wie viel Kupfer in jeder geätzten Lage verbleibt – also der Prozentsatz des Kupfers nach dem Ätzen. Der entfernte Kupferanteil entspricht dem Volumen, das das benachbarte Prepreg beim Schmelzen des Harzes ausfüllt.

- Die nominale Dicke der verwendeten Prepregs

Und weitere Parameter, wie Verpressparameter, Delta Werte vom Datenblatt Dk/Df zum wirklichen Wert. Der Delta vom Dk aus dem Datenblatt kann bis zu 0,5 abweichen.

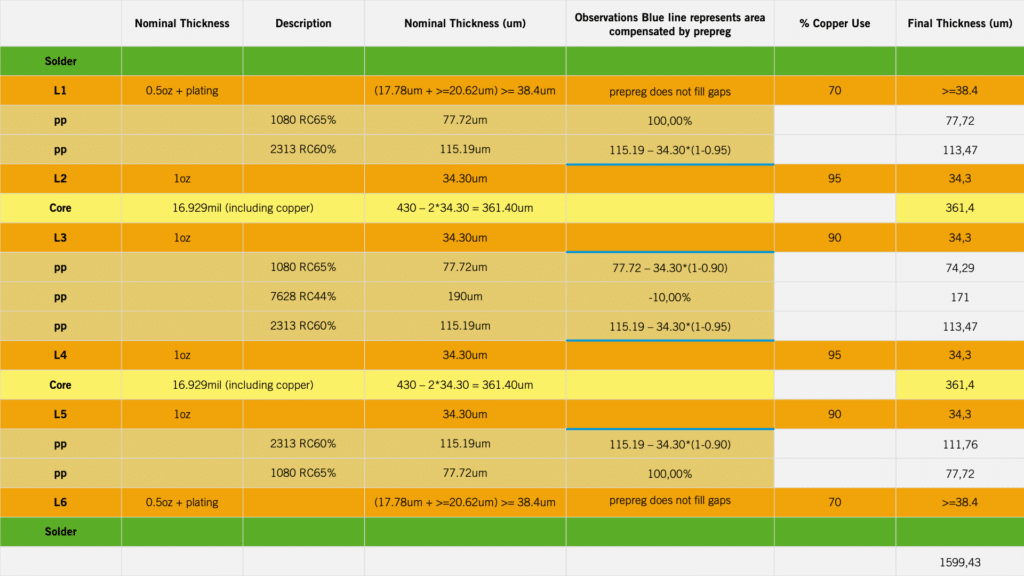

Die Aufbereitung und dessen Berechnung im Detail

Zurück zu unserer Ausgangssituation: Wie ergibt sich die endgültige Dicke, und wie werden diese Kompensationen berechnet? Sehen wir uns den Berechnungsprozess Schritt für Schritt an:

- Definieren Sie die Ausgangsdicken jeder Lage basierend auf den Designkriterien:

– Laminierte Kerne geben in der Regel die Dicke inklusive Kupfer an (abhängig vom Hersteller). Die tatsächliche Isolationsdicke erhält man, indem man die beiden Kupferfolien abzieht; hierfür müssen die Herstellerangaben geprüft werden. Vorsicht bei den Innenlagen, diese werden bei Standardaufbauten nicht mit Kupfer aufgalvanisiert (IPC-6012 Tabelle 3-17).

– Wählen Sie die anfängliche Prepreg-Dicke für jede Isolationslage entsprechend der gewählten Konfiguration – zum Beispiel die Dicke, die für eine kontrollierte Impedanz erforderlich ist.

– In den meisten Fällen werden die Dicken einfach so angepasst, dass die Gesamtdicke von 1,6 mm erreicht wird. - Berechnen Sie für jede Kupferlage den Prozentsatz des Kupfers, welcher stehen bleibt (nicht weggeätzt wird).

- Berechnen Sie die Kompensation, die durch die angrenzenden Prepregs erfolgt.

Bei NCAB unterstützen wir Sie bei diesen Berechnungen und stimmen uns mit der Fertigung ab, um die genauesten und realistischsten Anpassungen zu erzielen. - Überprüfen Sie, dass die Kompressionsreserve des Prepregs die empfohlenen Grenzwerte nicht überschreitet, damit das Glasfasergewebe im Inneren nicht übermäßig komprimiert wird. Die maximal zulässige Kompression wird vom Materialhersteller vorgegeben und vom Leiterplattenfertiger exakt eingehalten.

Die folgende Tabelle zeigt ein Beispiel, das die wichtigsten Punkte aus diesem Abschnitt veranschaulicht. Denken Sie daran: Die Anpassungsspielräume hängen vom jeweiligen Leiterplattenhersteller ab.

Die Spalte „Finale Endstärke (Final Thickness)“ zeigt die theoretisch resultierenden Dicken.

Darüber hinaus muss ein weiterer wichtiger Fertigungsaspekt berücksichtigt werden: die Dickenreduzierung, die durch Reinigung, ätzen, Polieren usw. der Kupferfolien entsteht. Diese Grenzwerte sind in IPC-6012 festgelegt – Tabelle 3-18 für äußere Kupferstärken und Tabelle 3-17 für innere Kupferlagen.

Zusammenfassung

Wir hoffen, dass die hier vorgestellte Vorgehensweise zur Anpassung des Stackups mehr Klarheit für Entwickler schafft. Gleichzeitig möchten wir betonen, wie wichtig es ist, den Leiterplattenhersteller in diesen Prozess einzubeziehen – denn er kennt das praktische Verhalten der Materialien und weiß, wie stark die eigenen Fertigungsprozesse die Enddicke von Kupfer und Prepreg beeinflussen, insbesondere bei Lagenaufbauten mit impedanzdefinierten Leitungen.

Eine Impedanzkontrolle bedeutet für den Hersteller zusätzlichen Aufwand: Es muss ein Impedanz-Coupon mitgefertigt und anschließend gemessen werden.

Bei NCAB haben wir strenge Vorgaben: Einmal freigegebene Leiterplatten dürfen nicht verlagert werden, und weder das Material noch die Produktionsstraße dürfen geändert werden. Dadurch können wir berechnete Lagenaufbauten mit sehr hoher Genauigkeit impedanzdefiniert produzieren. Das heißt: Wir passen den Lagenaufbau und die Leitergeometrien an und fertigen die Leiterplatte ohne zusätzliche Impedanzkontrolle. Unsere jahrzehntelange Erfahrung zeigt, dass wir damit die Zielwerte zuverlässig erreichen – und gleichzeitig die Kontrollkosten einsparen. Dieses Vorgehen stimmen wir mit unseren Kunden ab, wenn es keine normativen Vorgaben bzgl. Impedanzkontrolle gibt, wie z.B. bei Medizintechnik oder Defenseanwendenungen, bei welchen eine Impedanzkontrolle zwingend und dokumentiert sein muss.

Wir unterstützen Sie gerne bei der Definition des optimalen Stackups für Ihre neuen Designs. So stellen wir sicher, dass Ihr Layout perfekt an die Fertigungsprozesse angepasst ist, Produktionsprobleme vermieden werden und die Skalierbarkeit bis zur Serienfertigung gewährleistet ist.

Kontaktieren Sie einfach Ihren lokalen Ansprechpartner der NCAB Group für alle Fragen rund um Leiterplatten – wir helfen Ihnen gerne weiter.

The article is translated by Hüseyin Anaç, Field Application Engineer.

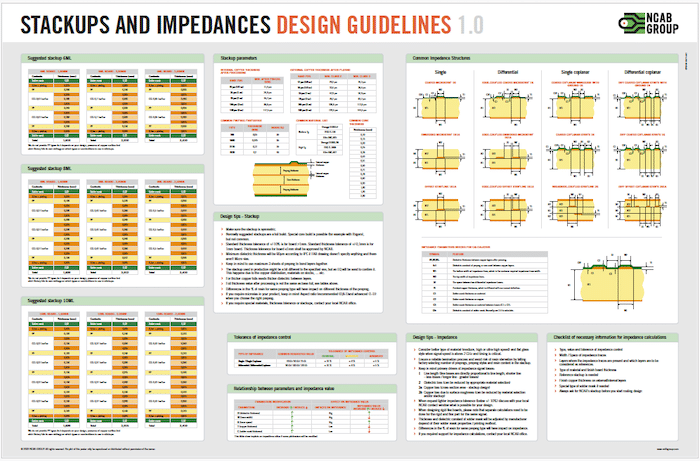

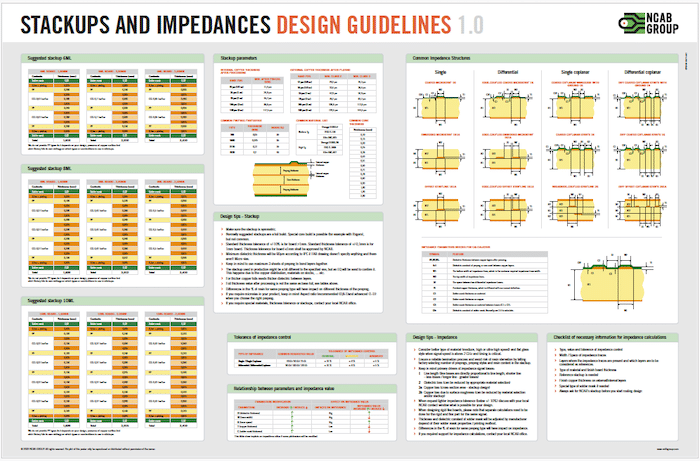

Laden Sie unsere Designrichtlinien für Stackups und Impedanzen herunter.

Zusätzlich bieten wir Richtlinien für Multilayer-PCBs, HDI-PCBs, Ultra-HDI-PCBs, Flex- und Starrflex-Leiterplatten, Semi-Flex-PCBs sowie Technologien wie Copper Coin und Via Protection – alles, um sicherzustellen, dass Ihr Design von Anfang an perfekt umgesetzt wird!