Nachstehend haben wir einige der am häufigsten gestellten Fragen, und Aspekte, die oft Gegenstand von Diskussionen sind, zusammengefasst. Hier können Sie auch Ihre Leiterplatten-Frage stellen.

HDI

Was ist eine Microvia-Bohrung?

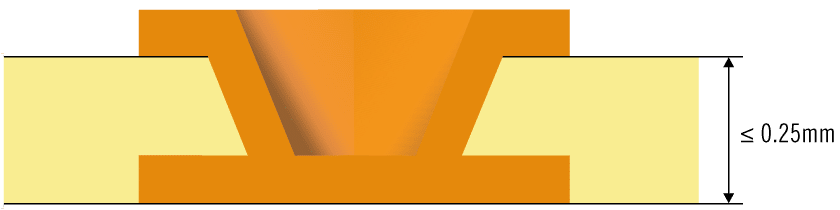

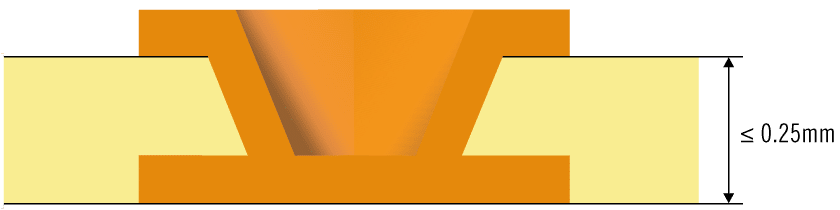

Gemäß der neuen Definition laut IPC-T-50M handelt es sich bei einer Microvia-Bohrung um eine Blindviastruktur mit einem maximalen Aspekt Ratio von 1:1, die an einem Zielpad mit einer Gesamttiefe von max. 0,25 mm endet, gemessen von der Anschlusspadfolie der Struktur bis zum Zielpad.

Was versteht man unter einem Blind Via?

Hierbei handelt es sich um eine Bohrung, die von einer Außenlage zur Innenlage reicht, jedoch nicht durch die gesamte Leiterplatte führt. Solche Durchkontaktierungen können mechanisch oder mittels Lasertechnologie gebohrt werden.

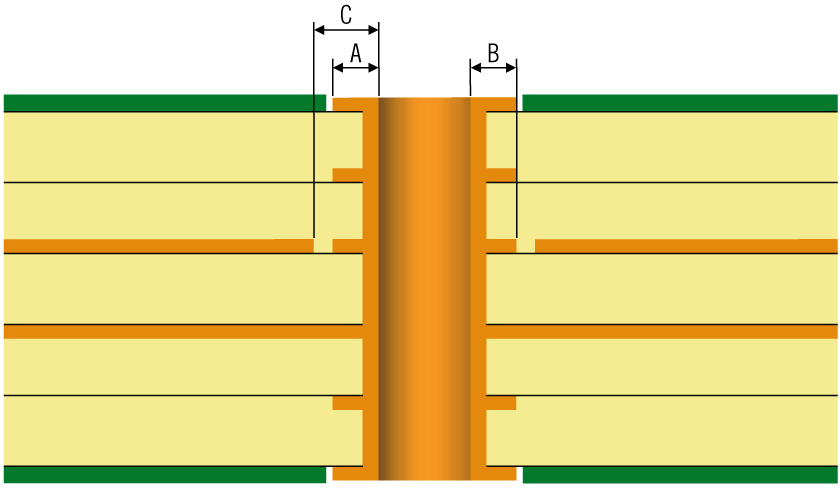

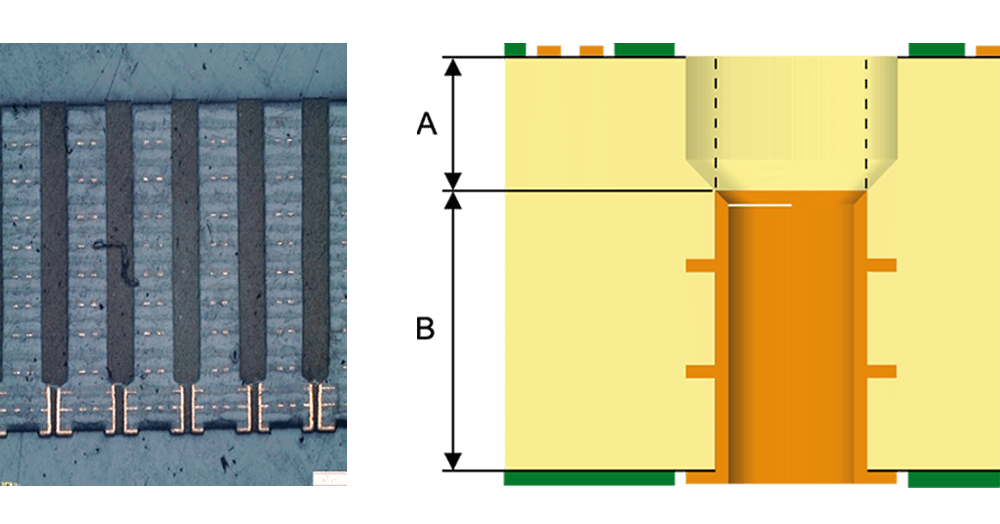

Die Abbildung unter Punkt 1 zeigt ein mittels Laser gebohrtes Blind Via.

Was versteht man unter einem Buried Via?

Hierbei handelt es sich um eine Bohrung zwischen einer oder mehrerer Innenlagen. Solche Durchkontaktierungen sind üblicherweise mechanisch gebohrt.

Was ist eine HDI-Leiterplatte?

IPC-2226 definiert HDI (High Density Interconnect) als Leiterplatten, bei denen die Verdrahtungsdichte pro Flächeneinheit höher liegt als bei herkömmlichen Leiterplatten. Sie besitzen feinere Bahnen und Abstände ≤ 100 µm / 0,10 mm, kleinere Vias (< 150 µm) und Lötpads 20 Pads/cm2) als Leiterplatten, die in herkömmlicher Leiterplattentechnik gefertigt werden.

Was ist eine Ultra-HDI-Leiterplatte?

Um als Ultra-HDI-Leiterplatte zu gelten, muss sie die folgenden Eigenschaften aufweisen:

- Leiterbahnbreiten und Isolationsabstände unter 50 µm

- Dielektrische Dicken unter 50 µm

- Microvia-Durchmesser unter 75 µm

- Produkteigenschaften, die den bestehenden IPC 2226 Level C Standard übertreffen

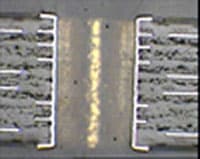

Gibt es unterschiedliche Arten von HDI-Merkmalen?

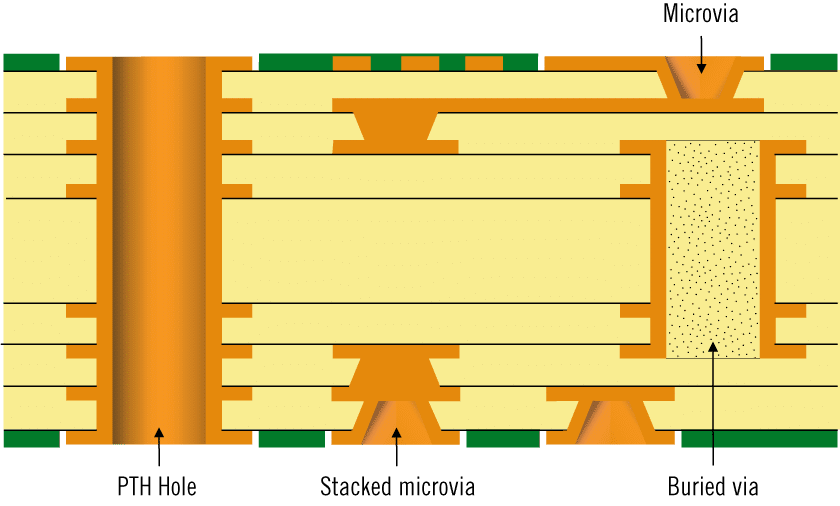

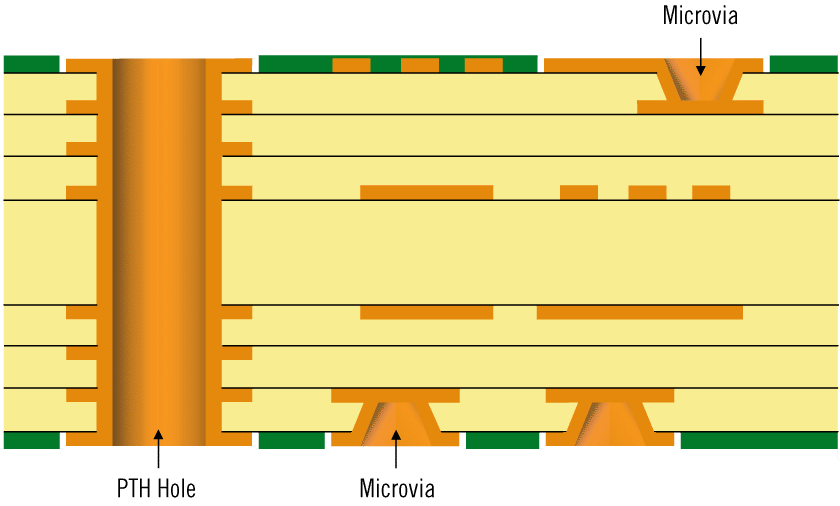

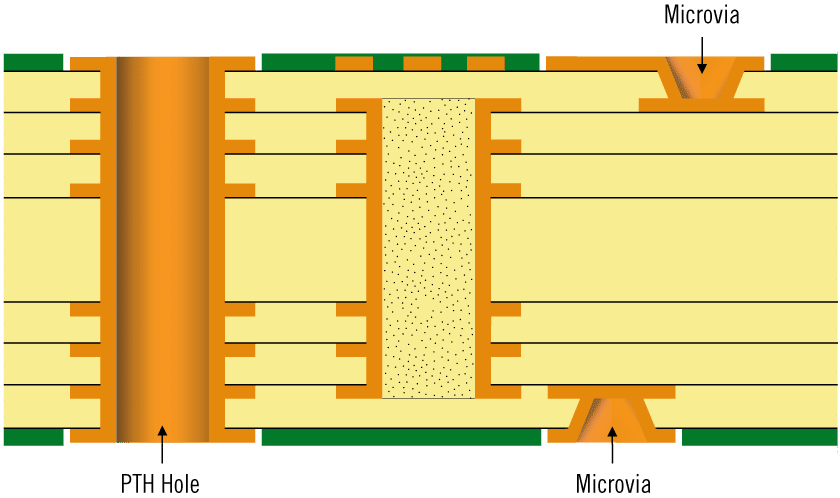

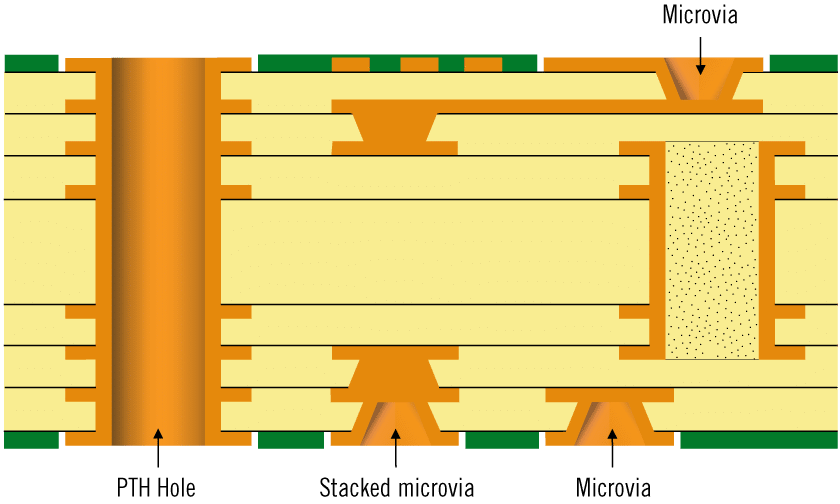

Die Abbildung unten zeigt die Hauptstrukturen – Typ I, Typ II und Typ III, wie in IPC-2226 definiert.

Type I. Definiert eine einzelne Microvia-Lage entweder auf einer Seite oder auf beiden Seiten des Kerns. Nutzt sowohl metallisierte Microvias als auch PTH (Durchkontaktierungen) für Verbindungen, wobei Blind Vias (Sacklöcher), aber keine Buried Vias (vergrabene Löcher) verwendet werden.

Type II. Definiert eine einzelne Microvia-Lage entweder auf einer Seite oder auf beiden Seiten des Kerns. Nutzt sowohl metallisierte Microvias als auch PTH für Verbindungen. Verwendet Blind und Buried Vias.

Type III. Definiert mindestens zwei Microvia-Lagen auf einer der beiden Seiten oder auf beiden Seiten des Innenteils. Nutzt sowohl metallisierte Microvias als auch PTH für Verbindungen. Verwendet Blind und Buried Vias.

Fachterminologie, um die Art des HDI-Aufbaus zu definieren:

- 1+n+1 = Einzellage von Microvias (wie in den Beispielen für Typ I und Typ II oben)

- 2+n+2 = 2 Microvia-Lagen (wie im Beispiel für Typ III oben)

- 3+n+3 = 3 Microvia-Lagen

FLEX/STARRFLEX

Welche Aufbauarten sind für Flex- und Starrflex-Leiterplatten verfügbar?

Es gibt eine Vielzahl verschiedener Aufbauarten, die zur Verfügung stehen. Die gängigsten davon sind im Folgenden aufgeführt:

Einseitige flexible Leiterplatte (IPC-60103 Typ 1, Polyimid plus Klebeschicht), mit einem nichthaftenden einseitigen FPC-Kern verbunden. Mit und ohne Versteifung.

Doppelseitige flexible Leiterplatte (IPC-6013 Typ 2), mit einem nichthaftenden zweiseitigen FPC-Kern (zwei leitfähige Lagen) mit Durchkontaktierungen. Mit und ohne Versteifung.

Mehrlagige flexible Leiterplatte (IPC-6013 Typ 3), beidseitig mit einer nichthaftenden Konstruktion aus drei oder mehr Kupferlagen mit Durchkontaktierungen. Mit und ohne Versteifung. Unsere Fertigungskompetenz beträgt 4 Lagen.

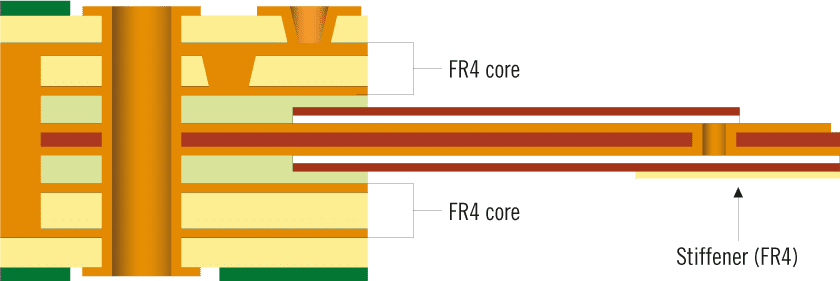

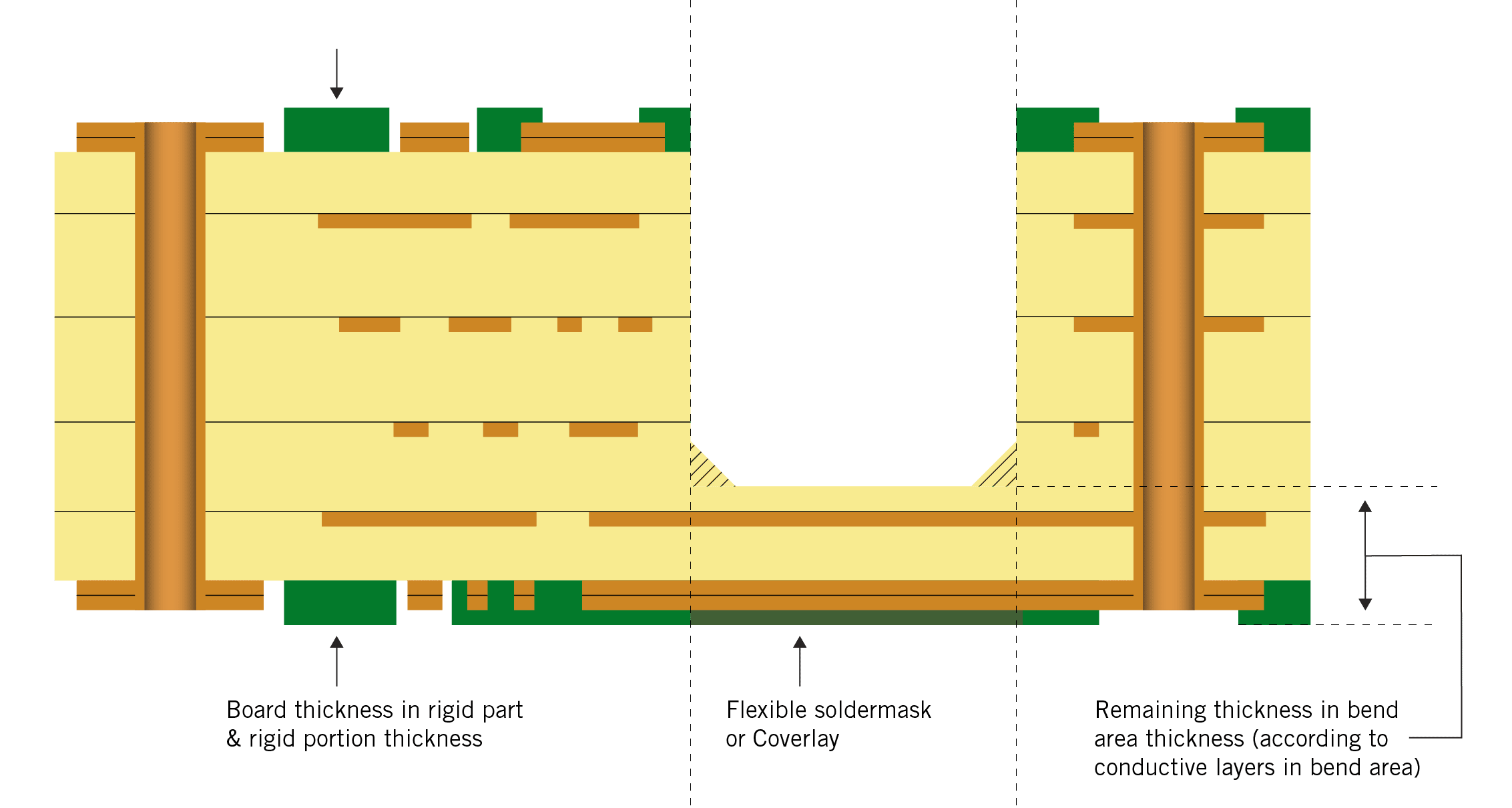

Starrflex-Konstruktion (IPC-6013 Typ 4) zur Kombination mehrlagiger Starr- und Flex-Lagen, die drei oder mehr Kupferlagen mit Durchkontaktierungen enthält. Unsere Fertigungskompetenz beträgt 22 Starr-Lagen mit bis zu 10 Flex-Lagen.

Asymmetrische Starrflex-Konstruktion, bei der sich der Flexübertritt auf der Außenlage befindet. Enthält 3 oder mehr Lagen mit Durchkontaktierungen.

Mehrlagige Starrflex-Konstruktion mit Buried/Blind Vias (Microvias) als Bestandteil der Starr-Konstruktion. Es werden bis zu zwei Microvia-Lagen erreicht. Bei einem homogenen Aufbau kann die Konstruktion auch zwei Starr-Strukturen als Bestandteil enthalten. Unsere Fertigungsfähigkeit beträgt 2 + n + 2 HDI-Strukturen.

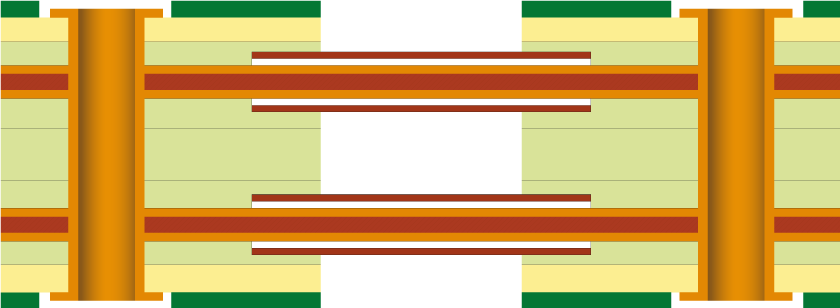

Aufbau mit Buchbindertechnologie (Luftspalt imFlex-Teil – komplexe Konstruktion).

Abstände zwischen den Flex-Lagen ermöglichen einen erhöhten Biegeradius des Flex-Teils. Bei der Buchbinderkonstruktion können die Flex-Lagen verschiedene Längen aufweisen, um die Kompression der inneren Flex-Lagen innerhalb des Biegeradius zu minimieren.

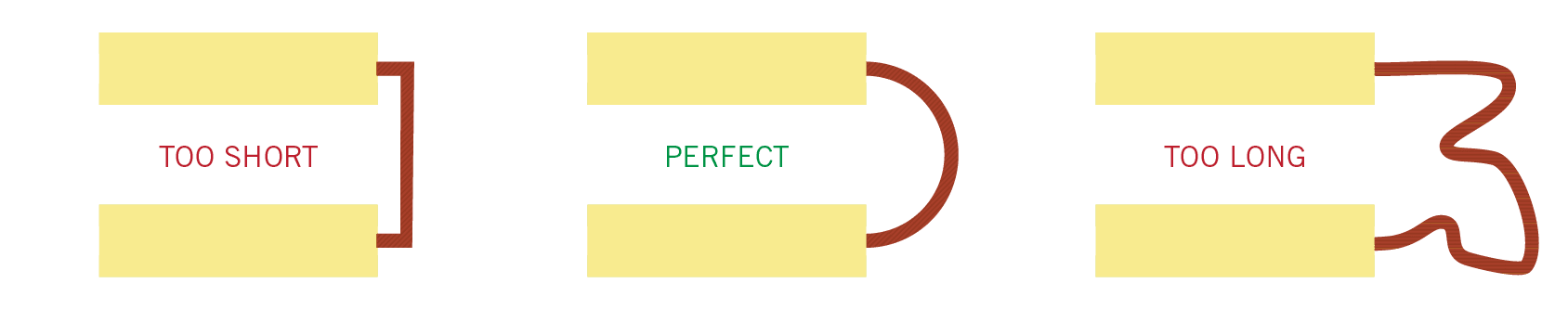

Wie wird die richtige Länge eines Flex-Teils der Starrflex-Konstruktion berechnet, um den minimalen Biegeradius zu berücksichtigen?

Detaillierte Empfehlungen finden sie in der IPC-2223 (Unterpunkt: 5.2.3.3). Diese gelten für Flex mit hohen Biegezyklen sowie für Flex zum einmaligen Einbau (engl. Flex to Install). Generell kann man sich nach der Faustformel gemäß der Endstärke des Flex-Bereiches richten (siehe unten).

| FLEX TYPE | MINIMUM BEND RADIUS |

|---|---|

| Single sided flex | 3 – 6 x circuit thickness |

| Double sided flex | 7 – 10 x circuit thickness |

| Multilayer flex | 10 – 15 x circuit thickness |

| Dynamic application | 20 – 40 x circuit thickness |

Worin besteht der Unterschied zwischen Semi-Flex-Leiterplatten und Starrflex-Leiterplatten?

Bei Semi-Flex-Leiterplatten handelt es sich im Prinzip um eine „normale“ mehrlagige Leiterplatte, die mittels spezieller FR4-Typen konstruiert wurde. Diese wurden auf eine spezifische Toleranz vertieft (Z-Achsen-Fräsung), sodass die resultierende dünnere Fläche den Flex-Part bildet. Semi-Flex ist für den einmaligen Einbau vorgesehen oder für eine sehr geringe Anzahl von Biegezyklen geeignet.

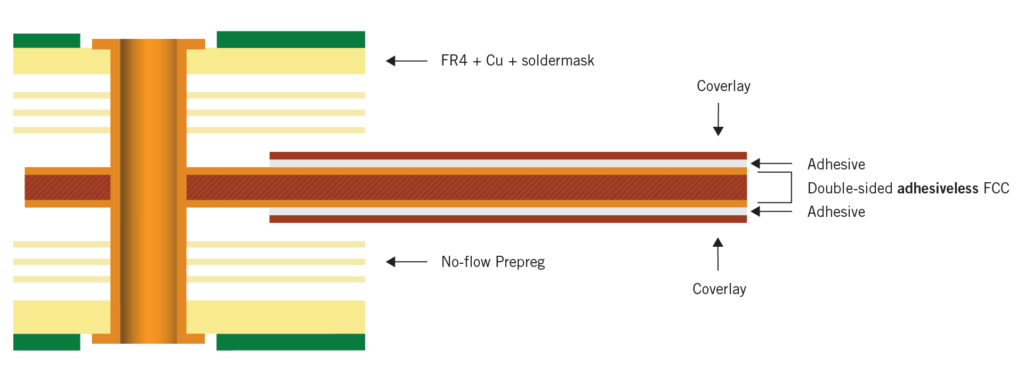

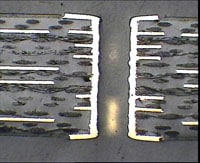

Worin besteht der Unterschied zwischen verklebten und verpressten Flex-Lagen?

Bei einem Aufbau aus verklebten Systemen wird die Verbindung zwischen dem Kupfer und dem flexiblen Kern durch die Klebeverbindung hergestellt. Daher dringt der Klebstoff bei diesem Aufbau entlang der gesamten Deckschicht in die Starr-Konstruktion und in die Bohrungen ein. Der höhere Ausdehnungskoeffizient des Klebstoffes erhöht das Risiko von Problemen bei der Durchkontaktierung, zum Beispiel in Form von Rissen und defekten Durchkontaktierungen, die aus der Ausdehnung resultieren. Außerdem kann die Präsenz des Klebstoffes in der Durchkontaktierung selbst zu Problemen bei der Aufkupferung an der Lochwandung führen, was der schlechten Entfernbarkeit der Klebstoffrückstände geschuldet ist.

Die Zuverlässigkeit der Vias/Durchkontaktierungen wird dadurch verbessert, indem man bei einer direktverpressten Kupferkaschierung auf den FPC-Kern verpresst, da kein Klebstoff in die Bohrung eindringt oder in den Starr-Teil austritt. Bei Starr-Flex-Konstruktionen ist dies das mit Abstand am häufigsten eingesetzte Konzept.

DESIGNRICHTLINIEN

Was ist die Mindestpadgröße für eine Bohrung in der Außen-/Innenlage?

Dies variiert von Hersteller zur Hersteller, im Allgemeinen kann man jedoch sagen, dass die Mehrheit der Hersteller diese wie folgt herstellen:

A = 0.15 mm

B = 0.20 mm

C = 0.30 mm

Wenn ich dickere Leiterbahnen als der Standard benötige, welche Leiterbahnbreiten kann ich verwenden?

Im Allgemeinen gilt, je dicker die Kupferbasis, desto breiter muss die Leiterbahn sein. Eine Faustregel ist, dass die Bahn bei einer 18 µm-Kupferbasis nicht schmaler als 0,1 mm (4 mil) sein sollte, und bei einer 105 µm Kupferbasis nicht schmaler als 0,25 mm (10 mil).

Welche Endschichtstärke des Kupfers ist zu erwarten?

Ein häufiges Missverständnis besteht darin, dass ein bestimmtes Kupfergewicht eine bestimmte, exakte Dicke ermöglicht, und dass die Dicke bei der Herstellung einer Leiterplatte nicht mehr abnimmt. Zum Beispiel 1 Unze = 35 µm oder 0,5 Unzen = 18 µm.

IPC-6012 legt jedoch die zulässige Mindestdicke sowohl von Kupferfolie als auch von Endschichtdicken nach Galvanik basierend auf zulässigen Toleranzen von Kupferfolien sowie der Reduzierung der Kupferbeschichtung im Rahmen der nachfolgenden Prozessschritte fest.

Im Folgenden sind einige Kupfergewichte und zulässigen Enddicken aufgelistet, die eher dem Standard entsprechen.

Aus diesem Grund ist es entscheidend, den eigenen Bedarf genau zu kennen und exakt zu spezifizieren. Andernfalls kann es zur Unter- oder Überspezifikation kommen, was zusätzliche Kosten verursachen kann, die sich im Design niederschlagen. Wenden Sie sich an unsere Techniker, um genauere Informationen zu erhalten.

| Foliendicke der Innenlage nach der Verarbeitung | |

| Basiskupfergewicht | Mindestenddicke nach Verarbeitung |

| 1/2 oz. | 11.4 um |

| 1 oz. | 24.9um |

| 2 oz. | 55.7um |

| Außenleiterdicke nach Beschichtung und Verarbeitung | ||

| Basiskupfergewicht | Mindestenddicke nach Verarbeitung Klasse 2 | Mindestenddicke nach Verarbeitung Klasse 3 |

| 1/2 oz. | 33.4um | 38.4um |

| 1 oz. | 47.9um | 52.9um |

| 2 oz. | 78.7um | 83.7um |

Sollten nicht-angeschlossene Pads beibehalten oder entfernt werden?

In IPC-2222A Punkt 9.1.4 ist klar festgelegt, dass der Hersteller diese nicht entfernen darf. Viele Herstellungsbetriebe fragen jedoch nach der Erlaubnis zum Entfernen dieser Pads, um bei der Produktion eine höhere Ausbeute zu erreichen. Wenn sie für die Funktion nicht von Bedeutung sind, empfehlen wir, die Erlaubnis zu ihrer Entfernung zu erteilen.

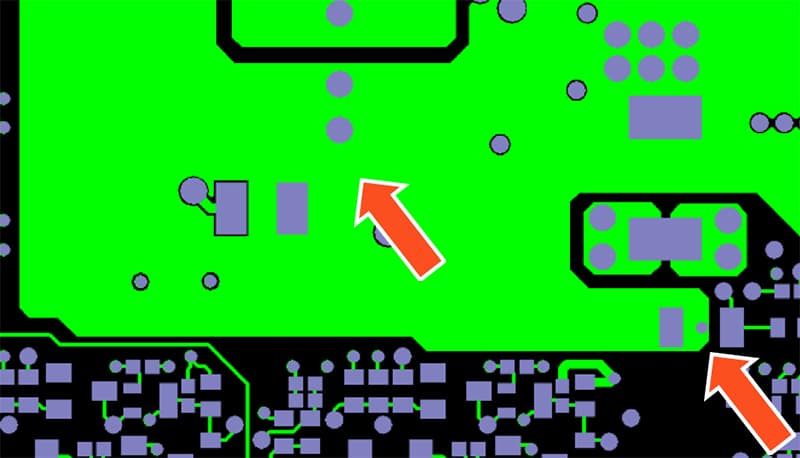

Was bedeutet Abstände im gleichen Netz?

„Abstände im gleichen Netz“ bedeutet, dass der Abstand von Kupfer zu Kupfer innerhalb desselben elektrischen Netzes zu gering ist, um gemäß den Gerberdateien produziert werden zu können. Da es sich um ein und dasselbe Netz handelt, schlägt der DRC (Design Rule Check) in der CAD-Software des Kunden bei diesem Fehler nicht Alarm. Es ist wichtig, dass der Kunde die Werte korrekt einstellt, wenn er ein neues Design beginnt. Der Mindestabstand von Kupfer zu Kupfer ist normalerweise korrekt eingestellt, aber es wird versäumt, denselben Wert einzustellen, wenn es sich um dasselbe Netz handelt. Es ist kein großes Problem, aber es führt zu Verzögerungen und unnötigen technischen Fragen.

Warum ist bei nicht-durchkontaktierten Löchern (NPTH) ein so großer Abstand vom Lochrand zum Kupfer erforderlich?

Wenn Sie Löcher in die Leiterplatte bohren, sollten Sie alle Löcher in der gleichen Aufspannung bohren, um die beste Positionsgenauigkeit für die Löcher zu erhalten. Die nicht-durchkontaktierten Löcher müssen dann während des Galvanisierungsprozesses abgedeckt werden (sonst werden sie ebenfalls durchkontaktiert). Um die nicht-durchkontaktierten Löcher abdecken zu können, benötigen wir einen Abstand zwischen dem Lochrand und dem Kupfer. Der erforderliche Abstand hängt von der Kupferstärke ab. Für eine Standardkupferdicke (18µm Basiskupfer) ist ein guter Abstand 0,3mm und definitiv nicht weniger als 0,2mm.

TERMINOLOGIE

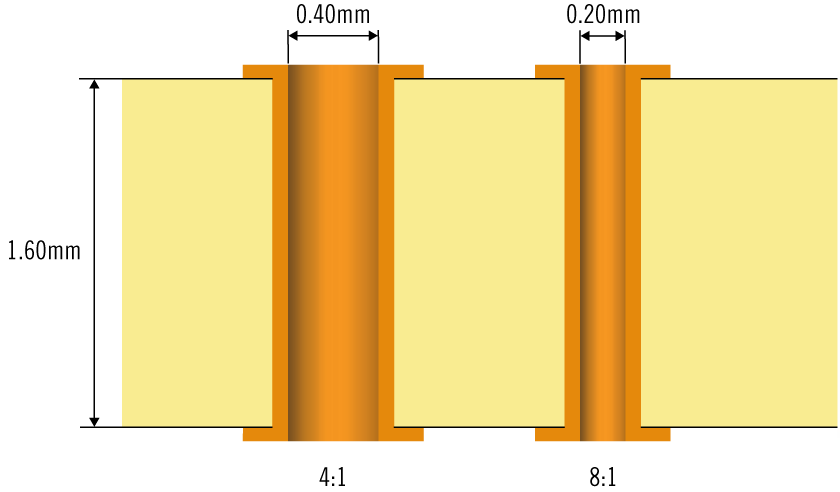

Was ist das “ aspect ratio ”?

Dies ist das Verhältnis zwischen dem Durchmesser der Bohrung und ihrer Länge. Wenn ein Hersteller von seiner Produktion sagt, dass sie ein „Seitenverhältnis“ von 8:1 aufweist, so bedeutet dies beispielsweise, dass der Durchmesser der Bohrung 0,20 mm bei einer Leiterplattenstärke von 1,60 mm beträgt.

Bei HDI-Strukturen beträgt das geeignete Aspekt Ratio für Microvias üblicherweise 0,8:1, wobei zur Vereinfachung der Metallisierung ein Verhältnis von 1:1 bevorzugt wird.

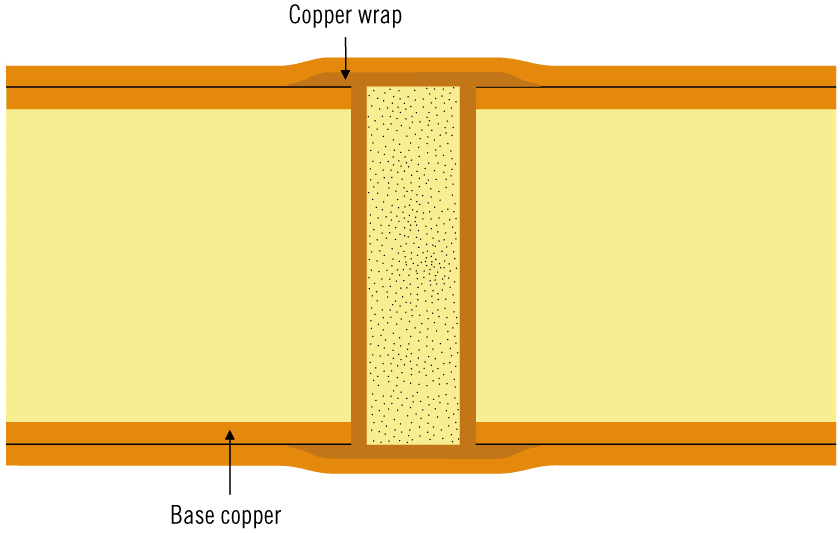

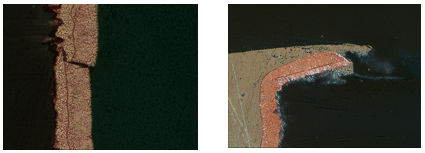

Was bedeutet Schulter-Metallisierung?

Als Schulter-Metallisierung wird eine durchgehende Beschichtung aus Kupfer bezeichnet, die im Hohlraum der Bohrung aufgebracht wird und bis zur Oberfläche der Leiterplatte (oder bei HDI-Aufbau bis zur Oberfläche des Kerns der Innenlage) reicht und sich auf der Oberfläche über mindestens 25 µm erstreckt.

Bei Klasse-2-Anforderungen muss die Dicke der Schulter-Metallisierung auf der Oberfläche mindestens 5 µm betragen. Bei Klasse-3-Anforderungen hängt dies davon ab, wo sich die Schulter-Metallisierung innerhalb des Aufbaus befindet. Wenden Sie sich an unsere Techniker, um genauere Informationen zu Klasse-3-Anforderungen zu erhalten.

Was ist eine „Copper Coin“-Leiterplatte?

Eine „Copper Coin“-Leiterplatte ist eine mehrlagige Leiterplatte, bei der jedoch ein massives Stück Kupfer, ein sogenannter Coin, in den Leiterplattenaufbau eingebettet ist. Dies ermöglicht eine direkte thermische Verbindung von einer Seite zur anderen oder von einer bestimmten Lage zu einer äußeren Lage.

Was bedeutet kontrollierte Impedanz?

Stellen Sie sich das Signal auf der Leiterplatte bei der Bewegung entlang einer Leiterbahn vor. Kontrollierte Impedanz bedeutet, dass wir den Wellenwiderstand entlang der Leiterbahn steuern. Dies steht mit dem Widerstand, der Kapazität und der Leitfähigkeit der betreffenden Leiterbahn in Zusammenhang.

Die Impedanz wird auch in Ohm gemessen. Sie unterscheidet sich vom Widerstand, der eine Eigenschaft des Gleichstroms ist. Die Impedanz ist eine Eigenschaft des Wechselstroms, was bedeutet, dass sie von der Frequenz abhängt.

Gibt es mehrere Arten kontrollierter Impedanz?

Ja, es gibt mehrere Arten. Diese werden im Folgenden erläutert:

Differentielle Impedanz – Impedanz eines Leiterpaares mit gleichen und entgegengesetzten Polaritätssignalen – gleiche Amplitude in Gegentakt zueinander.

Gegentaktmodus (odd mode impedance) – Impedanz einer Seite eines Leiterpaares, die sowohl gleiche als auch entgegengesetzte Polaritätssignale aufweisen – gleiche Amplitude und Antiphase.

Gleichtaktmodus (even mode impedance) – Impedanz einer Seite eines Leiterpaares mit gleichen Signalen – gleiche Amplitude und gleiche Polarität.

Gleichtaktimpedanz (common mode impedance ) – Impedanz eines Leiterpaares mit gleichen Vorzeichen – gleiche Amplitude und gleiche Polarität.

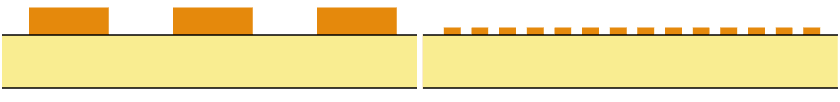

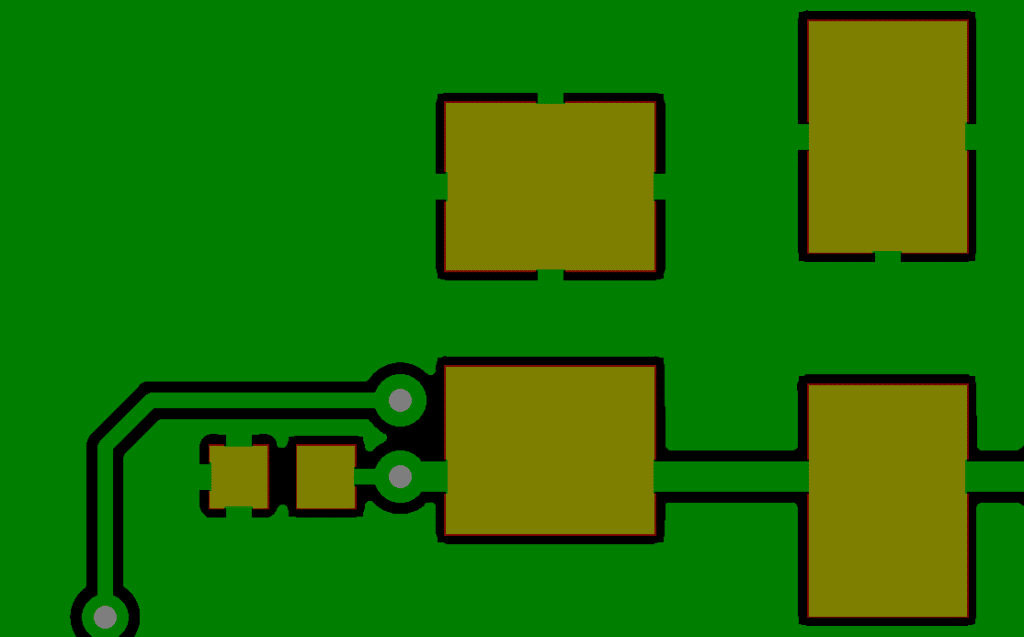

Was versteht man unter Wärmefallen bei Anschlussflächen für SMD-Komponenten?

Bei SMD-Komponenten, insbesondere bei kleineren, wird der Einsatz von Wärmefallen zur Simulation derselben thermischen Masse an allen Anschlusspunkten empfohlen. Hierdurch kann dem Grabsteineffekt, der Krümmung der Bauteile und etwaiger Beschädigungen von Bauteilen entgegengewirkt werden.

Bei Bauteilen mit Lochmontage (hole mounted, HMD) setzen wir auf den inneren Lagen thermische Entlastungspads ein, um die vollständige Benetzung des gesamten Kanals zu unterstützen. Die Formeln für thermische Entlastungspads finden Sie in der Dokumentreihe IPC-2220.

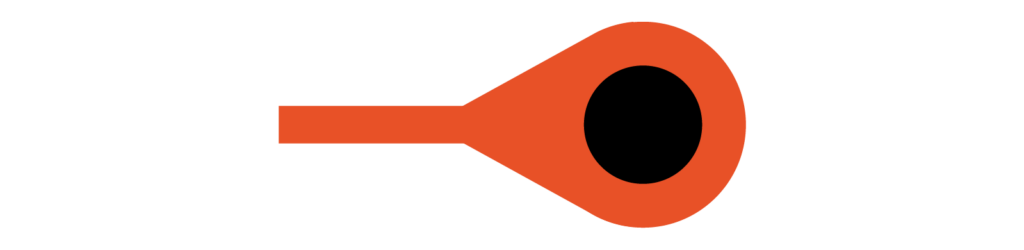

Muss die Genehmigung zum Hinzufügen von Teardrops in der Beschaffungsdokumentation aufgeführt werden?

In der neuen IPC-6012 D (Unterpunkt 3.4.2) darf der Leiterplattenfertiger die Leiterbahnanbindungen mit Teardrops verstärken, wenn die Leiterplatten nach Klasse 1 und 2 gefertigt werden sollen.

Wenn Sie keine Teardrops wünschen, sollten Sie dies in der Beschaffungsdokumentation explizit erwähnen. Achten Sie jedoch darauf, ausreichende Restringe hinzuzufügen.

Was ist die Backdrill-Technologie?

Bei Hochfrequenzanwendungen müssen Signalverluste vermieden werden. Wenn eine Lage mit einer anderen verbunden ist und das Signal von einer Lage zur anderen läuft, muss es eine Durchkontaktierung passieren, die beide Lagen miteinander verbindet. Wenn das Signal zum Beispiel bei einer Leiterplatte mit 20 Lagen von der ersten Lage zur zweiten Lage laufen muss, wird ein Teil der Durchkontaktierung als „überschüssig“ betrachtet. Bei dieser Anwendung ist es am besten, das überschüssige Kupfer aus dieser Durchkontaktierung zu entfernen, da es als Antenne wirkt und das Signal beeinträchtigt.

Wir setzen Backdrilling ein (kontrollierte Tiefe auf der Z-Achse), um das „überschüssige“ Kupfer in der Bohrung zu entfernen und dadurch bessere Signalstabilität zu erreichen. Je kürzer der Überstand ist („überschüssiges“ Kupfer), desto besser ist das Ergebnis. Der Durchmesser der Backdrill-Bohrung ist üblicherweise 0,2 mm größer als die entsprechende Durchkontaktierung.

| BACK DRILLING / COUNTER BORE (mm) | |||

|---|---|---|---|

| A: Depth tolerance | +/-0.20 | +/-0.15 | +/-0.10 |

| B: Min. remain thickness and tolerance | 0.5+/-0.25 | 0.35+/-0.1 | 0.3+/-0.1 |

Was versteht man unter Wärmewiderstand?

In diesem Video erfahren Sie mehr über den Wärmewiderstand und die Wärmeleitfähigkeit.

Wofür steht die „UL-Zulassung“?

Sicherheit ist in der Elektronikbranche von entscheidender Bedeutung. Anwender müssen sich unbedingt auf das Endprodukt verlassen können, was Brandsicherheit und elektrische Sicherheit angeht. Das bedeutet, dass sowohl die Leiterplatten als auch die Materialien, aus denen sie bestehen, höchsten Standards genügen müssen. Um die Konformität der Leiterplatten zu gewährleisten, ist es mittlerweile üblich geworden, den verwendeten Werkstoffen oder der Leiterplatte selbst eine UL-Zulassung zu erteilen.

Wofür steht UL überhaupt? Die Buchstaben UL stehen für „Underwriters Laboratories“. Warum ist die UL-Zulassung wichtig? UL ist eine wichtige Instanz und genießt einen guten Ruf in der Leiterplattenindustrie. Beim Test der Brandsicherheit und der elektrischen Sicherheit ist das Unternehmen unersetzlich. Kunden auf der ganzen Welt – einschließlich bekannter chinesischer Unternehmen – verlangen nach Herstellungsbetrieben, die in der Lage sind, eine UL-Zulassung zu erlangen. Daher ist der Besitz einer UL-Zulassung für Leiterplattenfabriken sehr wichtig, um sichere Leiterplatten herstellen zu können und Zugang zum internationalen Markt zu erhalten.

VIA HOLE

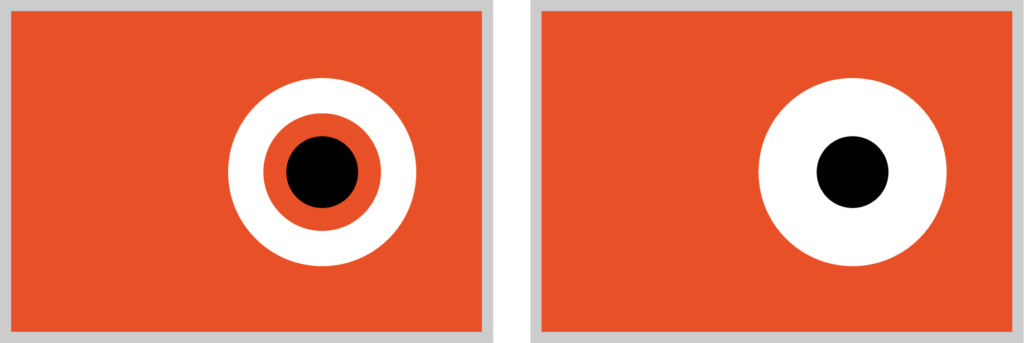

Welcher Verschluss wird für Durchkontaktierungen empfohlen?

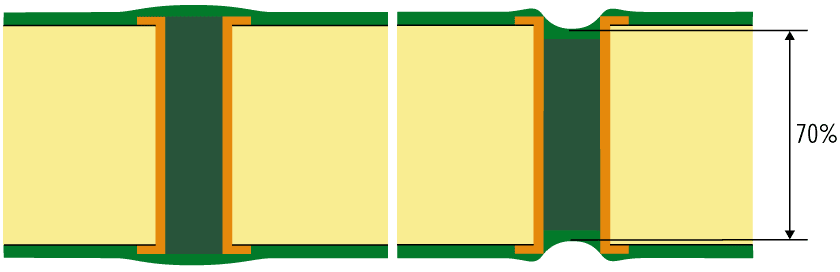

Der bevorzugte Verschlusstyp bei einem Standardprodukt (nicht bei gedeckelten Durchkontaktierungen) ist IPC-4761 Typ VI gefüllt und bedeckt, mit dem Ziel einer vollständigen Füllung, wobei gemäß Lastenheft der NCAB Group ≥ 70 % zulässig sind. Die nachstehende Abbildung stellt Typ VI mit einer flüssigen Stopplackabdeckung dar.

Ein nur einseitiger Verschluss wird nicht empfohlen (auch nicht Typ II überdeckt und abgedeckt) aufgrund von Bedenken hinsichtlich chemischer Einschlüsse bzw. der Wahrscheinlichkeit, dass bei HASL-Lacken (LF und SnPb) Lötkugeln auftreten können.

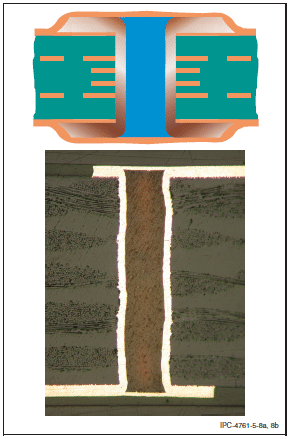

Was ist eine gedeckelte Durchkontaktierung?

Durchkontaktierungen werden als gedeckelt bezeichnet, wenn über der Via-Bohrung eine Kupfer-Beschichtung aufgebracht wird, sodass die Oberfläche vollständig metallisiert ist. Bei Klasse-2-Anforderungen beträgt die Dicke der Kupfer-/Padbeschichtung mindestens 5 µm, bei Klasse-3-Anforderungen 12 µm.

Dies richtet sich danach, ob als Füllmaterial Epoxidharz oder Stopplack verwendet wird, da durch Epoxidharz die Gefahr von Blasenbildung und Ausdehnung der Füllung bei Lötvorgängen minimiert wird. Dies lässt sich als Typ VII gemäß IPC-4761 kategorisieren – gefüllte und gedeckelte Durchkontaktierungen. Diese Konstruktion wird üblicherweise bei Designs mit Vias im Pad und bei BGA-Anwendungen eingesetzt, die eine hohe Dichte erfordern.

MATERIAL

Muss ich beim bleifreien Löten FR4-Material mit einer hohen Tg (Tg = Glasübergangstemperatur) verwenden?

Nicht unbedingt. Hierbei müssen viele Faktoren berücksichtigt werden, z. B. die Anzahl der Lagen und die Dicke der Leiterplatte, und es werden genaue Kenntnisse zum Montagevorgang benötigt (Anzahl der Lötzyklen, Zeitdauer über 260 Grad Celsius usw.). Untersuchungen haben gezeigt, dass ein Material mit einem „standardmäßigen“ Tg-Wert leistungsmäßig sogar besser abschneiden kann als Materialien mit einem höheren Tg-Wert. Berücksichtigen Sie hierbei auch, dass der Tg-Wert selbst beim Löten „mit verbleitem Zinn“ überschritten wird.

Am wichtigsten ist hierbei das Verhalten des Materials bei Temperaturen über dem Tg-Wert („post Tg“). Es ist also hilfreich, die Temperaturprofile zu kennen, denen die Leiterplatte ausgesetzt wird, um die notwendigen Leistungseigenschaften bestimmen zu können.

Welche Materialeigenschaften müssen bei der Auswahl des Materials berücksichtigt werden?

Wir würden als Erstes folgende Eigenschaften betrachten:

CTE (thermischer Ausdehnungskoeffizient)

Ein Maß dafür, wie stark sich das Material bei Erwärmung ausdehnt. Kritisch ist die Z-Achsen-Ausdehnung – üblicherweise über dem Tg-Wert, wo die Ausdehnung stärker ausfällt. Wenn der CTE nicht ausreicht, können Fehler bei der Bestückung auftreten, da sich das Material oberhalb von Tg schnell ausdehnt.

Materialien können denselben Tg-Wert und trotzdem verschiedene CTE-Werte besitzen – ein niedrigerer CTE ist besser. Ebenso können manche Materialien über höhere Tg-Werte verfügen, gleichzeitig jedoch einen höheren (schlechteren) CTE über dem Tg-Wert („post Tg“) aufweisen.

Tg / GLASÜBERGANGSTEMPERATUR

Der Tg-Wert ist die Temperatur, bei der ein Material vom relativ steifen, glasähnlichen Zustand zu einem elastischeren und biegsamen, kunststoffähnlichen Zustand übergeht. Dieser Wert ist wichtig, da sich oberhalb von Tg die Materialeigenschaften ändern.

Td / ZERFALLSTEMPERATUR

Dies ist ein Maß für die Zersetzung des Materials. Das Analyseverfahren ermittelt, wann 5 % des Materials gewichtsmäßig verloren sind – der Punkt, an dem die Zuverlässigkeit nicht mehr gewährleistet ist und Delaminierung auftreten kann.

Leiterplatten mit erhöhter Zuverlässigkeit erfordern eine Td ≥ 340 °C.

T260 / T288 / ZEIT BIS ZUR DELAMINIERUNG

Mit diesem Verfahren wird die Zeit ermittelt, nach der die Dicke der Leiterplatte bei einer vordefinierten Temperatur (in diesem Fall 260 oder 288 °C) irreversiblen Veränderungen unterliegt – d. h., wenn sich das Material so weit ausdehnt, dass Delaminierung auftritt.

Muss ich beim bleifreien Löten ein FR4-Material mit der höchsten Td (Td = Zerfallstemperatur) verwenden?

Ein höherer Td-Wert ist vorzuziehen, insbesondere wenn die Leiterplatte technisch komplex ist und einer Reihe von Wiederschmelz-Lötvorgängen unterzogen wird. Dies kann jedoch zu höheren Kosten führen. Kenntnisse zu Ihrem Montagevorgang helfen dabei, die richtige Entscheidung zu treffen.

Was ist der Unterschied zw. „Dicy“ und „NonDicy“ Härtersystemen für FR4 Epoxid?

Dicy (Dicyandiamine) ist bei weitem das gebräuchlichste Härtungssystem für Epoxy. Es ergibt typischerweise einen Td Wert von ca. 300–310°C während ein “nonDicy”, z.B. ein Phenolic Cured Epoxy, einen Td Wert von ca. 330–350°C ergibt; es erreicht damit eine höhere Temperatur-Festigkeit.

Was bedeutet „CAF“?

CAF (Conductive Anodic Filament) bedeutet eine elektrochemische Reaktion zwischen der Kupfer-Anode und Kathode, was zu einem Material-internem Kurzschluss führen kann.

Was ist die beste Leiterplattenoberfläche für bleifreies Löten?

Es gibt keine „beste“ Oberfläche; alle Oberflächen haben ihre Vor- und Nachteile. Welche gewählt werden sollte, hängt von vielen Faktoren ab. Für weitere Infos kontaktieren Sie bitte einen unserer Techniker oder besuchen Sie den Beitrag zu Leiterplattenoberflächen auf unserer Webseite.

Was sind die Regeln bzgl. Flammschutzmittel? Gibt es allgemeine Regelungen, nach denen das TBBP-A verboten wird?

Nein, eine Untersuchung ergab, dass aus praktischen Gründen kein Verbot existiert.

Was ist der Unterschied zwischen einem Flammschutzmittel, das als Reagenz hinzugefügt wird, im Gegensatz zu einem, das als als Additivum beigegeben wird?

Ein reaktives Flammschutzmittel ist chemisch an das Epoxidharz gebunden und löst sich bei der Entsorgung nicht auf bzw. tritt nicht aus.

Wie viele Reflow-Zyklen können FR4-Materialien aushalten?

Eine präzise Antwort lässt sich hierzu kaum geben. Wir haben jedoch Tests mit Materialien mit bis zu 22 Reflow-Verfahren durchgeführt, 4 davon mit einer Spitzentemperatur von 270 °C. Die Belastung nach 22 Reflows ist beträchtlich, und es besteht die Möglichkeit einer Materialschwächung, jedoch hielten sämtliche Verbindungen stand.

Wir empfehlen, ein Material mit einem hohen Tg-Wert zu wählen, wenn mehr als 6 Lagen vorhanden sind und diese dicker als 1,6 mm sind.

RoHS

Erfordert die RoHS bzw. WEEE Direktive eine Leiterplattenkennzeichnung?

Nein, aber aus praktischen Gründen sollten Leiterplatten mit bleifreier HAL-Oberfläche als RoHS kompatibel gekennzeichnet sein, um Unklarheiten mit verbleitem HAL zu vermeiden.

Sind RoHS-kompatible Leiterplatten auch halogen-frei?

Nein, nicht notwendigerweise. Die RoHS-Richtlinie verbietet zwei bromierte flame retardants, PBB (polybromided biphenyls) und PBDE (polybromided diphenyl ethers). Typischerweise in Leiterplatten verwendet wird das bromierte flame retardant mit der Bezeichnung: TBBP-A (Tetrabromobisphenol A).

Stellen Sie Ihre Leiterplatten-Frage

Wenn Sie die gesuchte Antwort nicht finden können oder mehr Details wünschen, dann kontaktieren Sie uns bitte und wir helfen Ihnen gerne weiter.

Ihre Kontaktinformationen werden gespeichert und dazu verwendet, Ihnen einen Link zu der Seite zu senden, von der Sie die Designrichtlinien herunterladen können. Die von Ihnen angegebene E-Mail-Adresse kann dazu genutzt werden, Ihnen Informationen zu senden, die möglicherweise für Sie von Interesse sein könnten. Ihre Kontaktinformationen werden ausschließlich von der NCAB Group genutzt. Indem Sie auf „Senden“ klicken, erklären Sie Ihr Einverständnis mit diesen Bestimmungen. Weitere Informationen zur Nutzung Ihrer persönlichen Informationen durch NCAB finden Sie in unseren Datenschutzrichtlinien.