Tabbed Routing ist eine innovative Routing-Methode, die von Intel entwickelt wurde, um dem begrenzten Raum auf Leiterplatten (PCBs) entgegenzuwirken, die oft nicht den erforderlichen Platz für Leitergeometrie (Leiterbreiten/Leiterabstand) bieten können.

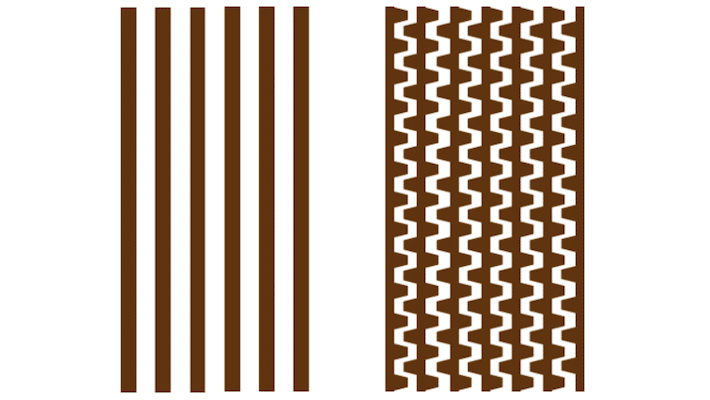

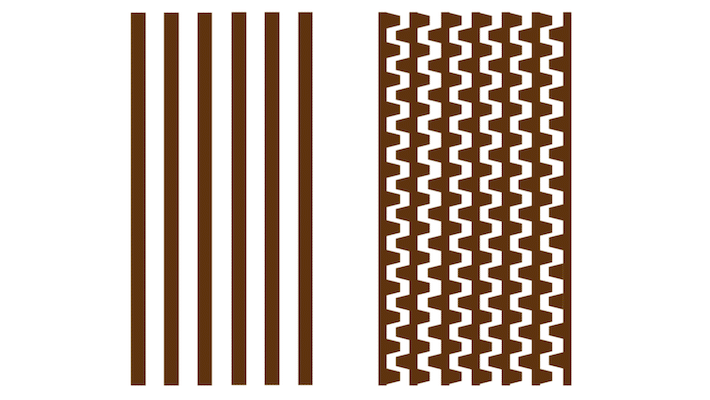

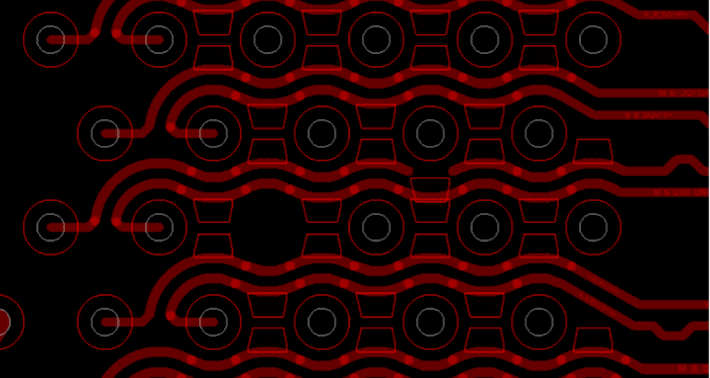

Diese Einschränkung kann zu schlechterer Signalintegrität und erheblichen Reflexionen und Crosstalk führen. Durch die effiziente Nutzung des Leiterplattenplatzes und die Einbindung kleiner Blöcke, sogenannter „Tabs“, in die Übertragungsleitungsstruktur verbessert das Tabbed Routing die Signalintegrität und reduziert Reflexionen und Crosstalk. Eine typische Struktur ist in der folgenden Abbildung dargestellt. Obwohl Tabbed Routing theoretisch auf jeden Bus angewendet werden kann, wird es aufgrund der spezifischen Routing-Herausforderungen, hauptsächlich in DDR-Bus-Anwendungen (Double Data Rate) eingesetzt.

Warum Tabbed Routing verwenden?

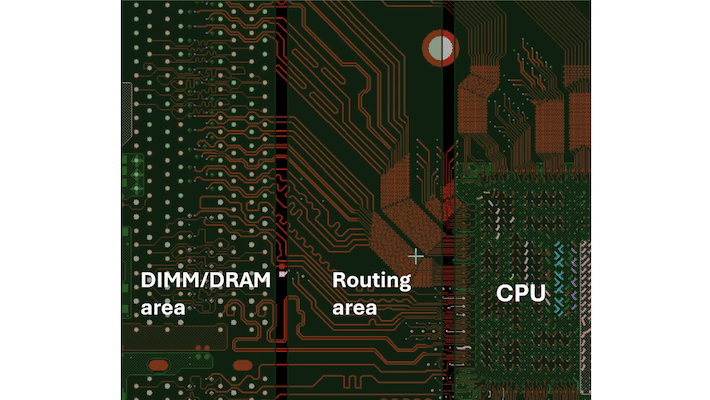

Betrachten wir das Gesamtschema bzgl. DDR zu CPU im Layout und dessen Entflechtung, das grob in drei Teile unterteilt werden kann:

- den CPU-Bereich, welcher in Pin-Field und Break-Out Bereich unterteilt ist

- den Routing-Bereich (Open Field Bereich)

- DIMM/DRAM-Bereich

Zunächst ist es wichtig, das Verdrahtungskonzept des DDR-Busses und wichtige Konzepte wie Pin-Feld, Breakout und Open Field zu verstehen.

Für dieses PCB-Layout wird eine Impedanz von 40 Ohm angenommen, was eine Leiterbreite von 152µm (6 mil) erfordert. Um die PDG-Anforderungen (Packaging Design Guidance) zu erfüllen, sollte der Leiterabstand 457µm (18 mil) betragen.

Das Pin-Feld bezieht sich auf den Bereich um die BGA-Pads und die entsprechenden Durchkontaktierungen im CPU/BGA-Bereich. Ein wesentliches Merkmal dieses Bereichs ist, dass ein großer Teil des PCB-Raums von BGA-Pads und den Durchkontaktierungen, die ihre Leiterbahnen verbinden, eingenommen wird, sodass nur begrenzter Platz für das Signal-Routing bleibt. Um alle Signalleiter in diesem begrenzten Raum unterzubringen, müssen schmalere Leiterbahnbreiten und reduzierte Abstände verwendet werden.

Aufgrund des begrenzten Platzes ist beispielsweise die Breite der Übertragungsleitung auf 89µm (3,5 mil) begrenzt. Im Vergleich zur Standardbreite von 152µm (6 mil) führt dies zu einer erhöhten Impedanz, wodurch eine Diskontinuität im Signalweg entsteht. Darüber hinaus ist der Leiterabstand tendenziell uneinheitlicher und im Allgemeinen kleiner – beispielsweise 200µm (4 mil) – als der Standardabstand von 457µm (18 mil), was das Signal-Crosstalk erhöht.

Das Fan-Out im BGA-Bereich, auch Pin-Feld genannt, dient als Ausgangspunkt für die Striplines, die auf die Innenlagen gelegt werden – eine gängige Methode, die insbesondere bei Mehrkanal-DDR-Layouts angewendet wird.

Bei diesem Ansatz werden die Leiterbahnen zwischen Durchkontaktierungen geroutet. Zwischen zwei benachbarten Durchkontaktierungen können nur zwei Signalleiter mit einer Breite von jeweils ca. 76µm (3,5 mil) und einem Abstand von 200µm (4 mil) geroutet werden. Diese Konfiguration führt zu einer höheren Impedanz. In einer idealen Stripline Anordnung wird erwartet, dass der Crosstalk im Fernbereich (Empfänger Ende [Far-End-Corsstalk]) relativ gering bleibt.

Der Abschnitt nach dem Pin-Feld wird als Breakout-Feld bezeichnet, das mehr Platz für die Entflechtung bietet. Aufgrund der hohen Dichte der DDR-Signalleitungen ist jedoch weiterhin ein spezieller Bereich erforderlich, um die Signalleitungen zu verteilen. Daher bleibt das Breakout-Feld etwas platzbeschränkt. In diesem Bereich werden in der Regel Leiterbahnen mit einer Breite von ca. 200µm (4 mil) und einem Abstand von ca. 400µm (8 mil) verwendet. Im Vergleich zum Standard-Routing – ca.250µm (6 mil) Breite und ca. 457µm (18 mil) Abstand – führt diese Konfiguration zu einer relativ hohen Impedanz und erhöhtem Crosstalk.

Nachdem die Signalleitungen im Breakout-Feld aufgefächert wurden, gelangen sie in einen breiteren Bereich, in dem das Routing stattfinden kann, das sogenannte offene Feld. In diesem Bereich folgt das Standard-Routing den Designregeln mit einer Leiterbahnbreite von ca.250µm (6 mil) und einem Abstand von ca. 457µm (18 mil). Beim DDR-Design sind Signalreflexion und Crosstalk die beiden größten Herausforderungen. Ingenieure und Designer müssen sich bemühen, eine konsistente Impedanz aufrechtzuerhalten und das Crosstalk so weit wie möglich zu minimieren.

Der herkömmliche Ansatz beim PCB-Design besteht darin, wo immer möglich Standardleitungsbreiten und -abstände zu verwenden. Das bedeutet, dass die Länge der Pin-Feld- und Breakout-Feld-Bereiche minimiert werden sollte. Im Idealfall würde das gesamte Routing dem Open-Field-Ansatz folgen, bei dem das Standard-Routing gemäß den Designregeln angewendet werden kann. Dies ist jedoch beim DDR-PCB-Design schwer zu erreichen, da es die Kosten erheblich erhöht, da zusätzliche Routing-Lagen erforderlich sind, um die BGA-Signalleitungen zu entflechten.

Wenn die Leiterlänge in den Pin-Feld- und Breakout-Feldbereichen nicht minimiert werden kann, empfiehlt Intel die Verwendung der Tabbed-Routing-Methode. Bei dieser Technik werden in diesen Bereichen Tabs hinzugefügt, um eine konsistente Impedanz aufrechtzuerhalten und das Crosstalk zu reduzieren.

Prinzipien und Simulationen des Tabbed-Routings

Wie oben erwähnt, erfüllt das Tabbed Routing zwei Hauptfunktionen:

- Reduzierung der Impedanz in diesem Bereich, Verbesserung der Impedanzanpassung und damit Verringerung der Signalreflexion.

- Reduzierung von Crosstalk zwischen Signalen, genauer gesagt, Reduzierung des Far-End-Crosstalks.

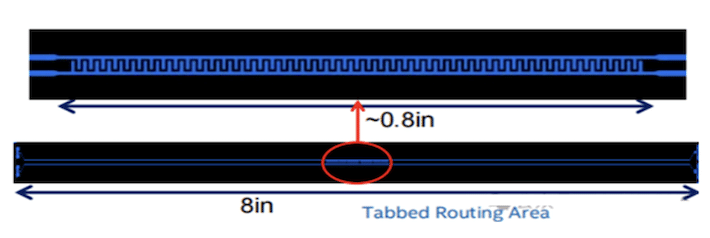

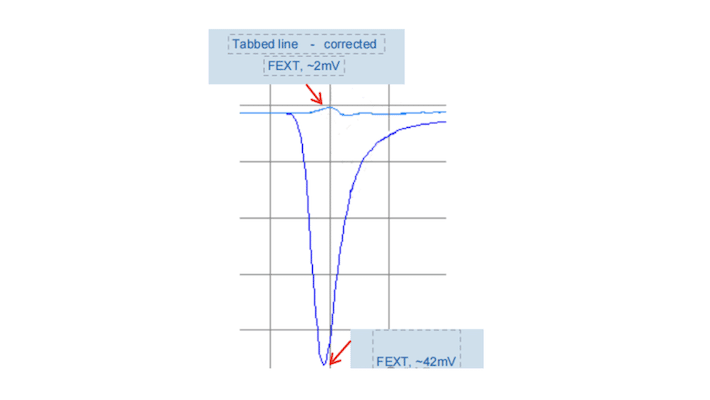

Der erste Punkt ist recht intuitiv: Durch Hinzufügen von Tabs wird die Leitungsbreite vergrößert, wodurch die Impedanz reduziert und an die Impedanz einer normalen Verlegung angeglichen wird. Die Wirkung des Hinzufügens von Tabs kann durch Simulation überprüft werden. Das folgende Beispiel stammt aus einer öffentlich zugänglichen Dokumentation von Intel. Bei einem Paar Mikrostripleitungen beträgt die Kopplungslänge ca. 20,32cm (8 Zoll).

Der Wert für das Far-End-Crosstalks sinkt von 42 mV auf 2 mV, wenn man die Ergebnisse mit und ohne Tab-Routing vergleicht. In tatsächlichen Projekten kann die Größe der Tabs jedoch aufgrund von Einschränkungen im PCB-Bereich nicht beliebig angepasst werden, sodass die Ergebnisse variieren können.

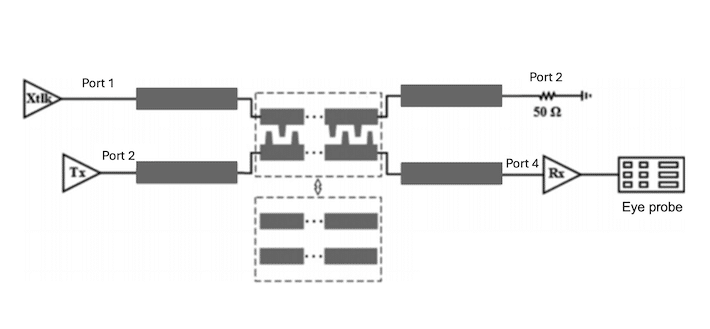

Die Auswirkung auf das Signal ist sehr gut im Eye-Diagramm nachvollziehbar. Nachfolgend finden Sie ein einfaches Beispiel für die Schaltung wie oben gezeigt.

Im Folgenden werden die Ergebnisse der Eye-Diagramm-Simulation vor und nach der Anwendung von Tabbed Routing verglichen. Die Ergebnisse zeigen, dass sich sowohl die Augenbreite als auch die Augenhöhe nach dem Hinzufügen des Routings in unterschiedlichem Maße verbessern (Flankenschwellen).

Tabbed Routing – Design und Anwendung

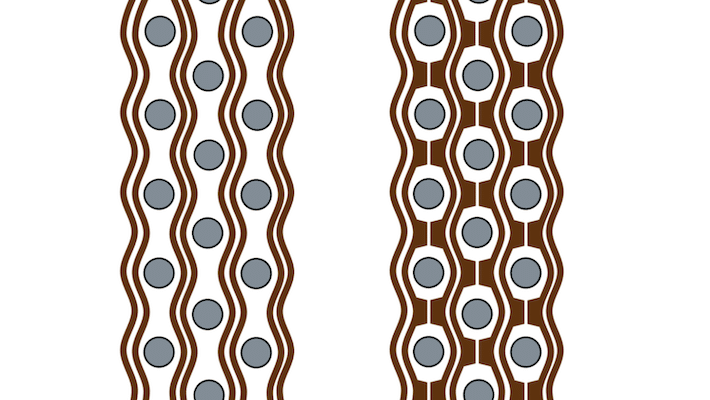

Im PCB-Design werden verschiedene Arten von Tabs in unterschiedlichen Bereichen eingesetzt, um die Signalintegrität und Impedanzanpassung zu optimieren. Nachfolgend sind verschiedene Arten von Tabs und ihre Unterschiede aufgeführt:

a. Interdigital tabs (breakout field):

b. In field tabs (pin field):

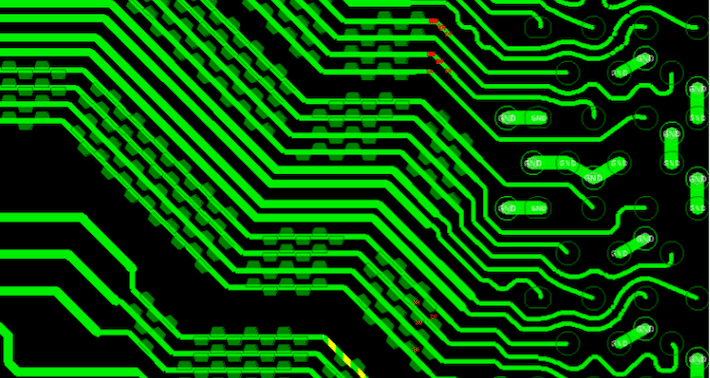

c. In tatsächlichen Designprojekten kann es je nach PCB-Form, Bauteilplatzierung und Routing-Bereich verschiedene Routing-Methoden geben:

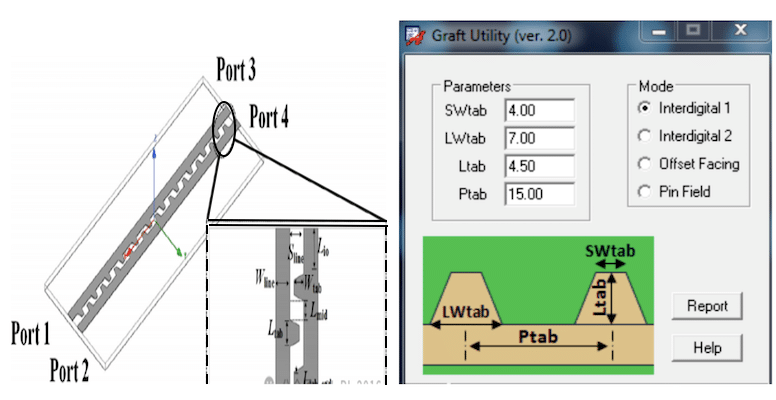

d. Tabbed Routing-Parameter – In Designprojekten enthalten PCB-EDA -Programme wie Allegro integrierte Plug-ins, mit denen das Tabbed Routing-Design durch einfache Eingabe der erforderlichen Parameter automatisch fertiggestellt werden kann.

Im Allgemeinen werden gegenüberliegende Tabs sowohl im Pin-Feld als auch im offenen Feld verwendet, um die gegenseitige Kapazität und Impedanz zu steuern und so die Signalintegrität zu verbessern. Pin-Feld-Tabs werden speziell für die Impedanzanpassung innerhalb des Pin-Feldbereichs verwendet, während Interdigital-Tabs hauptsächlich die Leiterbahndichte und das Übersprechen im äußeren offenen Feld beeinflussen.

Tipps zum Entwurf von DDR-Tab-Routing

- Konsistenz bei der Anzahl der Tabs: Innerhalb jeder DQ- oder DQS-Gruppe muss die Anzahl der Tabs konsistent sein, mit einer Toleranz von ±1. Wenn die Breakout-Länge eines DQ- oder DQS-Signals die Verwendung von Tabbed Routing nicht zulässt, sollte auch keines der anderen Signale in dieser Gruppe davon Gebrauch machen. Dadurch wird eine einheitliche Signalverzögerung über die gesamte Länge der Gruppe gewährleistet.

- Größe und Abstand: Die Größe und der Abstand der Tabs sollten auf der Grundlage spezifischer Faktoren wie Lagenaufbau, Leiterbahnlänge, verfügbarer Routing-Platz und anderer Designbeschränkungen festgelegt werden. Diese Parameter müssen durch Simulation überprüft werden, um eine optimale Impedanzanpassung und eine effektive Unterdrückung von Crosstalk sicherzustellen.

Ist das Tabbed Routing für Partikular-DDR geeignet?

- Chipbasierte DDRs zeichnen sich in der Regel durch ein kompakteres Layout mit einer kurzen Buslänge aus. Aufgrund ihrer Gehäuse und Peripherieanschlüsse verfügen sie möglicherweise nicht über einen so ausgeprägten Breakout-Bereich wie DIMM-basierte DDRs.

- Der Pin-Bereich von chipbasierten DDRs weist in der Regel kürzere Routing-Längen und einen kleineren Bereich mit Impedanzdiskontinuität auf, sodass Impedanzfehlanpassungen im Vergleich zu DIMM-basierten DDRs weniger problematisch sind. Daher ist der Bedarf an Tabbed Routing zur Behebung von Impedanzproblemen entsprechend geringer.

- Die Länge des Pin-Feldes kann bei verschiedenen DDR-Gehäusen variieren, was eine Standardisierung der Anzahl der verwendeten Tabs erschwert. Diese Variabilität beeinträchtigt die Konsistenz der Signalverzögerung und erhöht die Komplexität der Aufrechterhaltung einer genauen Längenanpassung.

- Chipbasiertes DDR bietet eine größere Flexibilität bei den Verdrahtungsmethoden und der Auswahl der Kupferlagen und erfordert nicht immer ein umfangreiches Oberflächen-Routing. Während das Tabbed-Routing bemerkenswerte Vorteile für die Reduzierung von Übersprechen und die Impedanzkontrolle beim Oberflächen-Routing bietet, sind diese Vorteile weniger ausgeprägt, wenn chipbasiertes DDR nicht stark auf Oberflächenschichten angewiesen ist.

- Im Allgemeinen wird DIMM-DDR typischerweise in Geräten wie Computern und Servern mit hohen Leistungsanforderungen und höheren Geschwindigkeiten verwendet, während chipbasiertes DDR häufiger in Geräten mit strengeren Platz- und Leistungsbeschränkungen zum Einsatz kommt. Diese Geräte haben in der Regel niedrigere Geschwindigkeiten, und die Probleme mit der Signalintegrität sind weniger kritisch.

Bei der Verwendung von Tabbed Routing im PCB-Design ist zu beachten, dass Tabs die Kopplung zwischen Signalleitungen erhöhen können. Wenn sie zu nahe an anderen Leiterbahnen platziert werden, kann das zusätzliche Kupfer die kapazitive oder induktive Kopplung verstärken, was zu erhöhtem Crosstalk führt. Schlecht konstruierte Tabs können auch bei bestimmten Frequenzen in Resonanz treten, wodurch hochfrequente Störgeräusche verstärkt und die Signalintegrität verschlechtert werden.

Um diese Risiken zu mindern, müssen Größe, Abstand und andere Parameter der Tabs durch Simulation sorgfältig optimiert werden. Dieser Designprozess ist komplex, und die Einbeziehung von Tabs erhöht die Schwierigkeit der Leiterplattenherstellung, was zu höheren Produktionskosten und -zeiten führt.

Schlussfolgerungen

Tabbed Routing ist eine innovative Designmethode, die von Intel für Szenarien entwickelt wurde, in denen der Platz für das PCB-Routing begrenzt ist. Sie ermöglicht eine Impedanzkompensation und reduziert das Far-End-Crosstalk in begrenzten Bereichen, wodurch die Gesamtsignalleistung verbessert wird. Tabbed Routing wird zwar häufig im DDR-PCB-Design verwendet, kann aber auch in Interposern und anderen Chip Bereichen eingesetzt werden.

Obwohl Tabbed Routing klare Vorteile bei Designs mit hoher Dichte und hoher Geschwindigkeit bietet, ist es für Schaltungen mit ausreichend Platz für das Routing, niedrigeren Signalraten oder weniger strengen Anforderungen an die Signalintegrität möglicherweise nicht erforderlich. In solchen Fällen rechtfertigen die Leistungsgewinne möglicherweise nicht die zusätzliche Komplexität des Designs und die höheren Herstellungskosten.

Referenzen:

1.Tabbed_Routing_Basics_563771_rev1_0, Intel

2.Cheng-Yu Tsai,etc, „Mitigate Package Level Crosstalk Using Tabbed Design”, in 2023 IEEE, 979-8-3503-8412-3

3. PCB-west-2016-new-techniques-address-layout-challenges-high-speed-routing-cp, Cadence.

The text is translated into German by Hüseyin Anaç, Field Application Engineer.

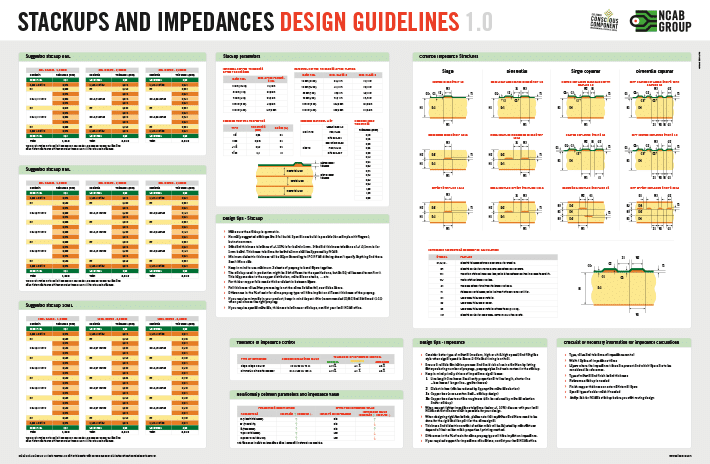

Laden Sie unsere Design Rules für Leiterplatten herunter

Und erhalten Sie weitere nützliche Informationen zum Entwurf zuverlässiger Leiterplatten. Diese sind verfügbar für mehrschichtige Leiterplatten, HDI-Leiterplatten, Ultra-HDI-Leiterplatten, flexible/starrflexible Leiterplatten, semi-flexible Leiterplatten, Copper Coins, Durchkontaktierungen und Stack-Ups sowie Impedanzen.