Diese Anforderungen entstehen, wenn man nicht mehr nur an ein einzelnes Objekt denkt, das eine einzige und einfache Funktion erfüllt, sondern an Objekte, die sich in Bezug auf Leistung und ästhetischem Erscheinungsbild weiterentwickeln und die Fähigkeit haben, mehrere Funktionen und Aufgaben auszuführen. Das klassischste Beispiel ist das Mobiltelefon. Von einer einzigen Funktion des Telefonierens hat sich dieses hin zu einem System entwickelt, das alles um uns herum verbindet.

Ein weiterer wichtiger Treiber zur Miniaturisierung elektronischer Bauteile ist die kontinuierliche Erhöhung von Datenvolumina und Übertragungsgeschwindigkeiten der Applikationen. Höhere Datenkapazität (Stichwort 5G) bedeuten kürzere Signal-Laufzeiten und höhere elektrische Frequenzen, was wiederum kompaktere Designs für kürzere Signallaufzeiten bedingt.

Aus diesem Grund entwickeln wir noch kleinere elektronische Boards mit höherer Leistung und mehr Funktionen, die gleichzeitig dünner und leichter sind. Dies erfordert einen sehr strickten Design- und Produktionsprozess, um eine optimale Leistung zu erzielen. Für diese Entwicklung braucht man Lösungen für eine höhere Verbindungsdichte und eine höhere Lagenzahl der Leiterplatte.

Durch das immer enger werdende Design steht weniger Platz für das Routing zur Verfügung, was zu kleineren Leiterbahnen und Leiterbahnabständen mit immer geringeren Durchmessern der Durchgangslöcher (Vias) führt.

Ein paar Anmerkungen zu HDI-Designs:

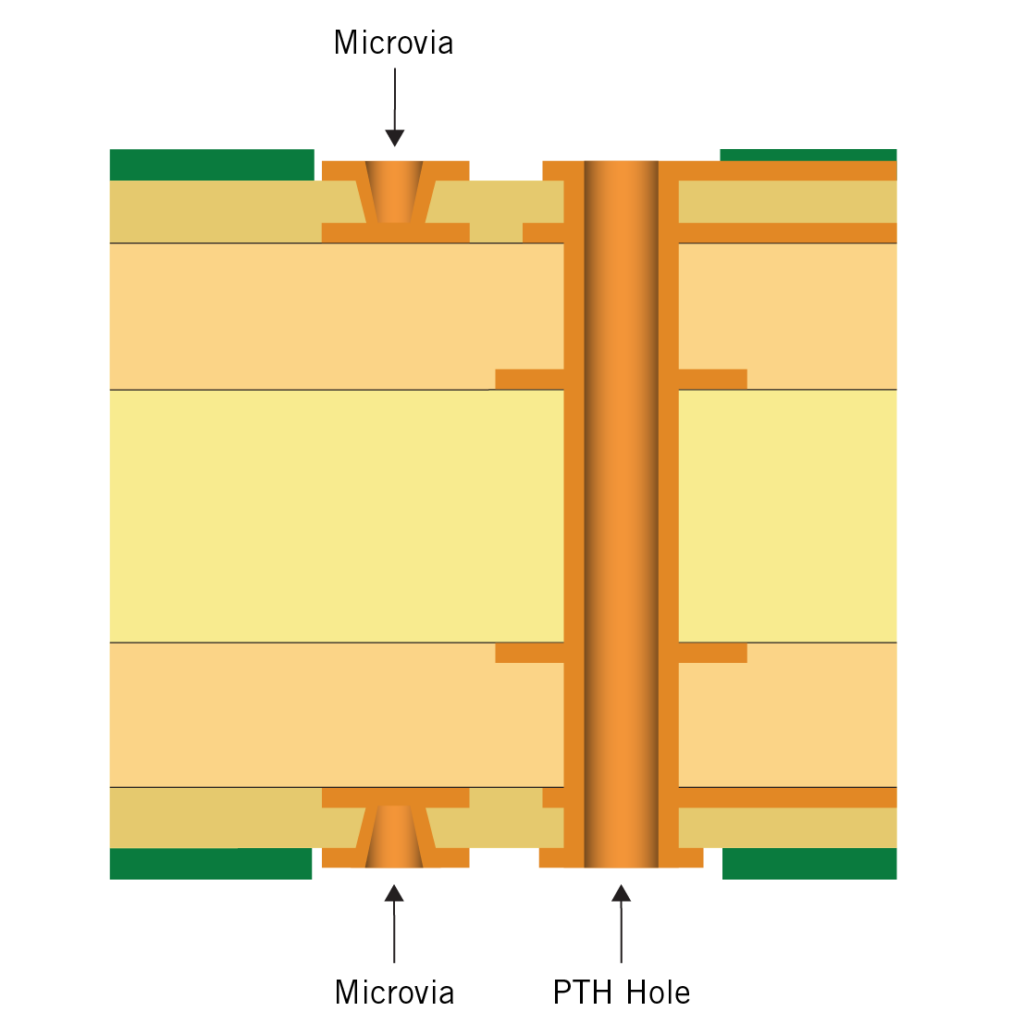

- Blind holes (Sacklöcher) sind Laserbohrungen auf den Außenseiten

- Buried holes (vergrabene Löcher) sind meist mechanisch gebohrte Verbindungen der Innenlagen

- Man benötigt auch dünnere Prepreg- und CCL-Laminate als herkömmliche Multilayer-Produkte

Wenn das Projekt an technische Grenzwerte stößt, ist klar, dass der gesamte Designprozess einige notwendige Richtlinien befolgen muss, vom Designer bis zum Leiterplattenlieferanten.

Die international anerkannte IPC ist dominierend bei der Definition dieser Richtlinien, indem sie auf Standards verweist:

- IPC-2226 betrifft den Design-Bereich

- IPC-6012 betrifft die Akzeptanzkriterien von starren Leiterplatten

- IPC-4104 deckt die verschiedenen leitenden und dielektrischen Materialen ab, die zur Fertigung von HDI-Boards verwendet werden können

- IPC-4101 betrifft die typischen Eigenschaften der Basismaterialien

Definition von HDI

Gemäß IPC-6012 ist eine HDI-Leiterplatte definiert durch eine durchschnittliche Anzahl von mindestens 20 elektrischen Verbindungen pro cm² auf beiden Seiten des Kerns. Um diese Bedingungen im Allgemeinen zu erreichen, dürfen Microvia-Leiterbahnbreiten und – Leiterbahnabstände 100µm nicht überschreiten. Wenn man bedenkt, dass diese Parameter für alle Lagen der Leiterplatte gelten, kann man ermessen, dass dies eine große technologische Herausforderung für den Leiterplattenlieferanten darstellt.

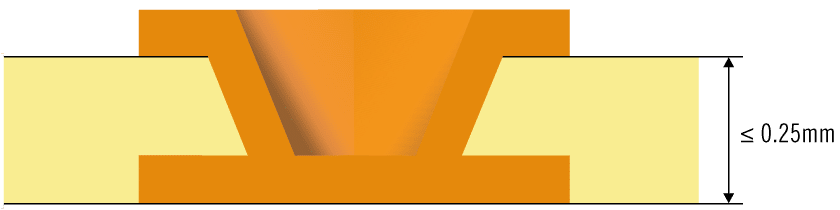

Die IPC-6012 definiert auch die Struktur eines Microvias.

- Ein Microvia ist eine Blindstruktur mit einem maximalen Maßverhältnis von 1:1 zwischen Lochdurchmesser und Lochtiefe (aspect ratio), mit einer Gesamttiefe von nicht mehr als 0,25 mm, gemessen von der Oberfläche zum Zielpad oder -ebene

- NCAB betrachtet eine Dicke des Dielektrikums zwischen Oberfläche und Referenzpad von 60 – 80µm als typisch

- Der Durchmesser eines Microvias liegt im Bereich von 80-100 microns. Das typische aspect ratio liegt zwischen 0.6:1 bis 1:1, idealerweise bei 0.8:1

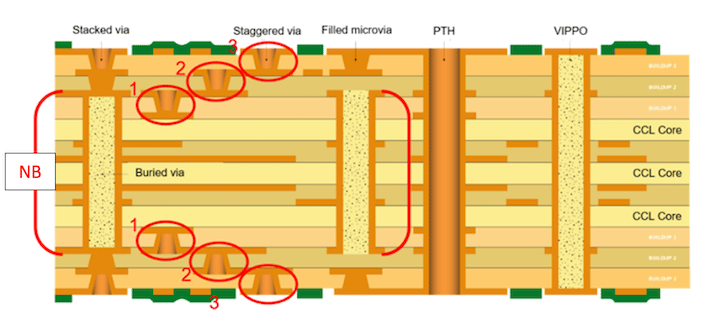

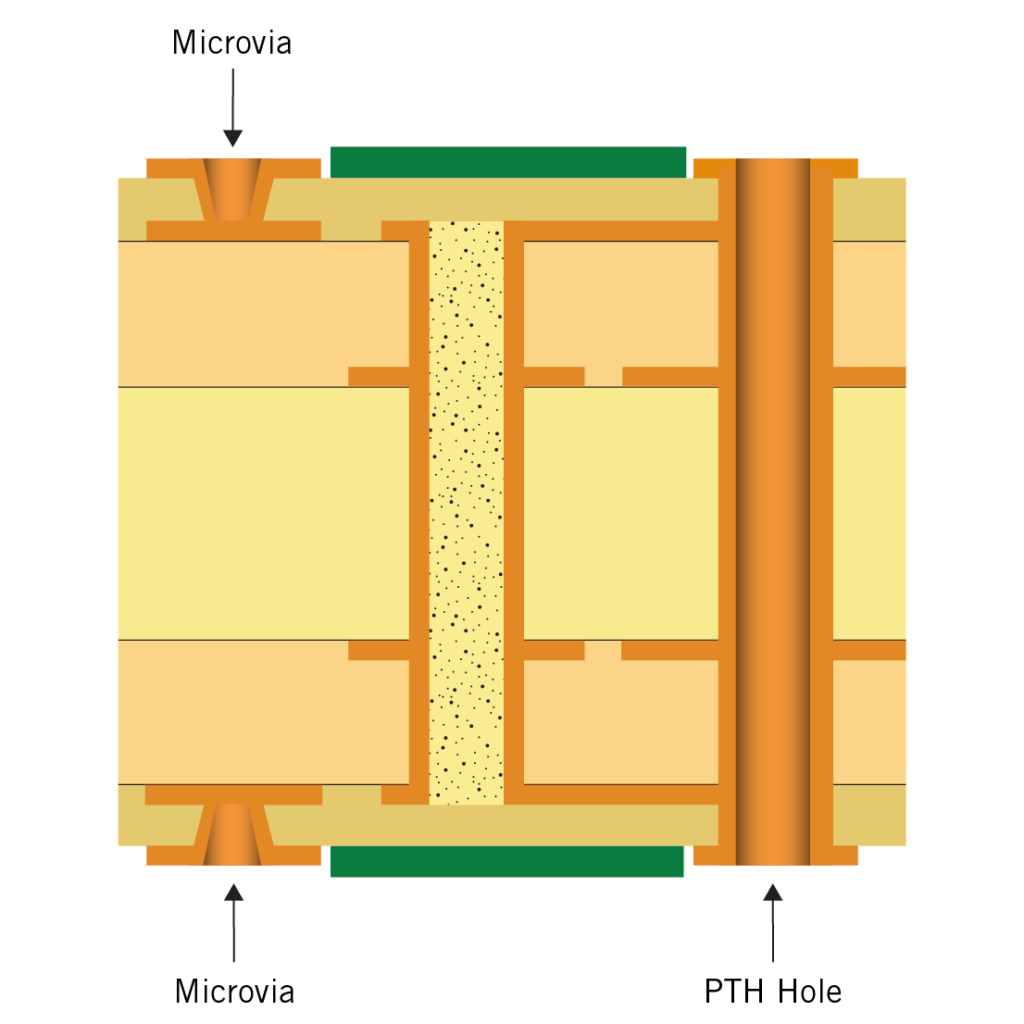

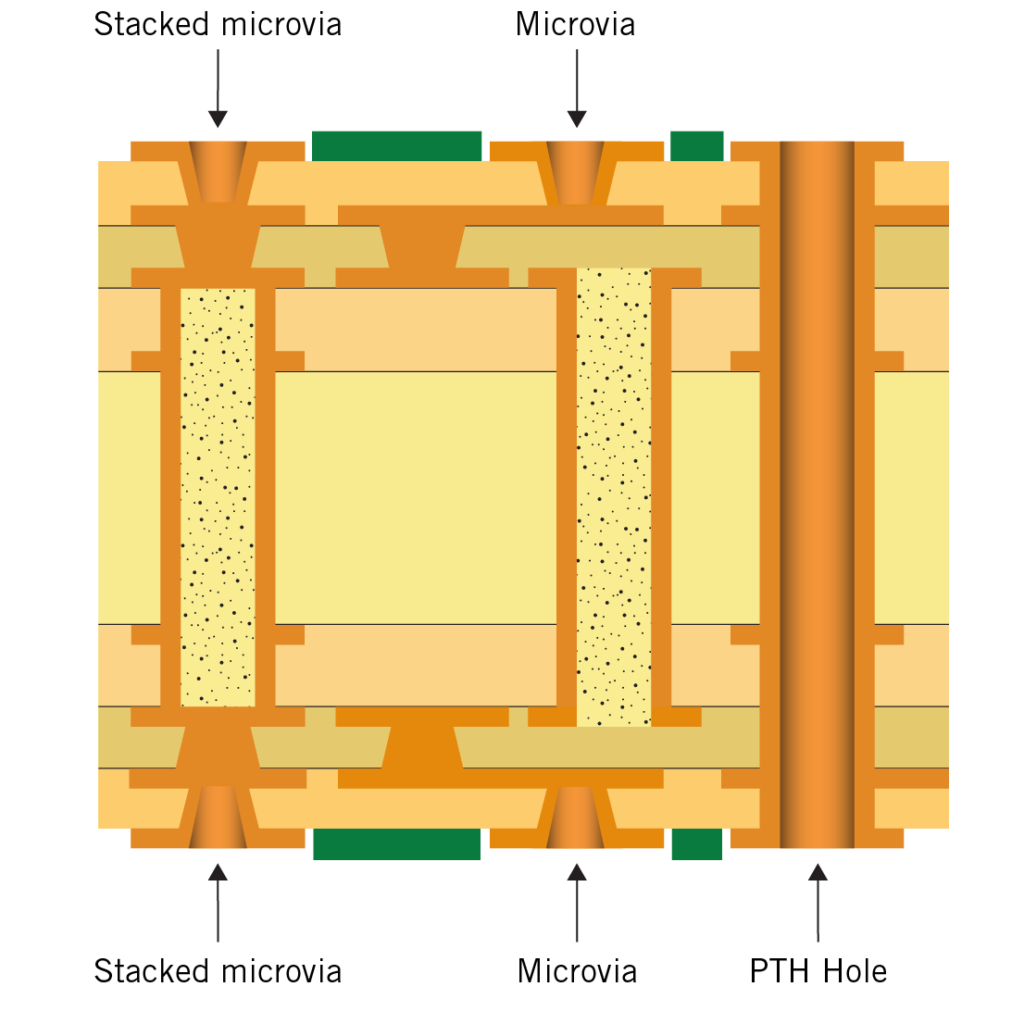

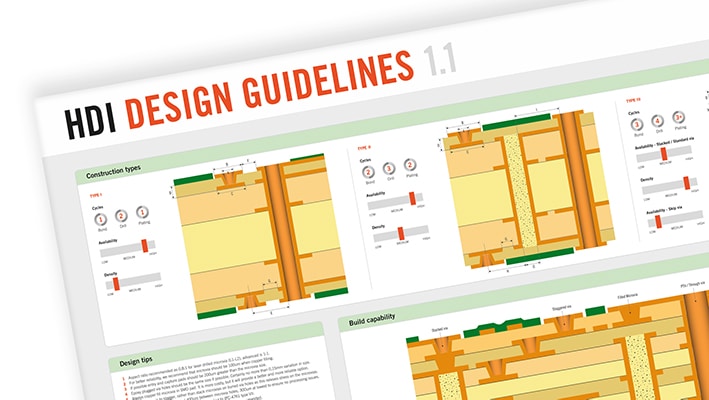

Die IPC-2226 definiert 3 Typen von HDI-Strukturen, die in den Bildern unten dargestellt sind.

- TYP 1 STRUKTUREN bestehen aus einer einzelnen Microvia-Lage, ein- oder beidseitig. Es können sowohl Microvias als auch Durchgangslöcher (Standard-Vias) vorhanden sein. Wichtig ist die Einhaltung des aspect ratios 0.8:1 für die Microvias. Diese Strukturen verwenden nur Blind Vias, keine Buried Vias.

- TYP 2 STRUKTUREN sind ähnlich zu Typ 1 und bestehen ebenfalls aus einer Microvia-Lage, ein- oder beidseitig. Abweichend sind aber neben Microvias und Standard-Vias auch Buried Vias vorhanden.

- TYP 3 STRUKTUREN sind die komplexesten und anspruchsvollsten für die Fabriken. Sie bestehen aus mindestens zwei Microvia-Lagen, ein- oder beidseitig. Wie bei Typ 2 können Microvias, Standard-Vias und Buried Vias vorhanden sein.

Warum HDI?

Wir kennen bereits die Gründe für HDI, nämlich die Technologie, die sich weiterentwickelt und alles in Bezug auf Komprimierung und Miniaturisierung an die technologischen Grenzen treibt. Aber was sind die Vorteile?

Es ermöglicht komplexere Designs in Bezug auf Platz und Verbindungen zu erstellen und Komponenten der neuesten Generation – einschließlich BGA-Pitch 0,4 mm und kleiner – einzusetzen. Diese Komponenten benötigen sehr viele Anschlüsse auf kleinstem Raum.

Zurückkommend zur Beschreibung von Microvia-Typen, die wesentlich für HDI Konstruktionen sind, finden wir Beispiele in einer Typ-III-Struktur (Abb. 1), die eng mit Parametern verknüpft sind, die durch die Designregeln gut definiert sind.

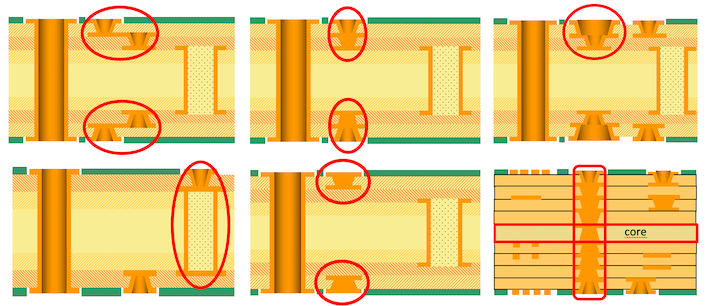

Microvias Staggered

Dies sind gestaffelte, nicht überlappende Microvias. In diesem Fall müssen die Buried Microvias nicht mit dem sogenannten „Copper Vias Filling“ – Verfahren gefüllt werden.

Microvias Stacked

Dies sind überlappende Microvias. In diesem Fall muss das Buried Microvia mittels des „Copper Vias Filling“- Verfahrens mit Kupfer gefüllt werden, ein Prozess, der für diese Technologie weit verbreitet ist.

Microvias Stepped

Dies sind überlappende Microvias. Diese eher ungewöhnliche Konstruktion ist charakterisiert durch zwei verschiedene überlappende Durchmesser von Blind Vias. Bei diesem Aufbau ist es nicht erforderlich, die erste Ebene der Buried Vias mit Kupfer zu füllen.

Microvias on Pad

Bei diesem Typ mit „Via-on-Pad“-Technik muss das vergrabene Loch immer mit Epoxidharz mit niedrigem CTE gefüllt und dann mit Kupfer abgedeckt werden. In diesem Fall handelt es sich um ein Verfahren nach IPC 4761 Typ VII.

Microvias filled on Pad

Bei diesem Typ werden die „Via-on-Pads“ mit dem „Copper Vias Filling“-Verfahren gefüllt. Dadurch können Bauteile der neuesten Generation mit sehr feinem Pin-Raster (fine pitch) direkt auf diese Pads gelötet werden.

Microvias ELIC

Bei diesem Typ überlappen sich die Microvias ausgehend von einem zentralen Kern. Der Aufbau des Objekts erfolgt sequentiell im Laserbohrverfahren und im „Copper Vias Filling“-Verfahren SBU (sequential build up).

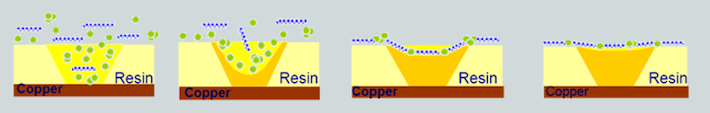

„Copper Vias Filling“-Prozess

Warum ist dieser Prozess für eine HDI-Leiterplatte wichtig?

Die klar erkennbaren Vorteile liegen in der Wärmeableitung und der unterstützten höheren Stromtragfähigkeit. Mittlerweile hat die Kombination von Implantaten und chemischen Prozessen zu einer besseren Planarität der Pads beigetragen. Dies ermöglicht während der Montage der Komponenten ein zuverlässiges Verlöten von Komponenten der neuesten Generation.

Unten sind die Ergebnisse einzelner Prozessphasen dargestellt.

Zur Erzielung eines guten Ergebnisses ist die richtige Kombination von Prozess und Design wichtig:

- Hohe Qualität der Laserbohrung, sauber und frei von ausfransenden Glasfasern

- Sehr genaue Kontrolle des Rückätzens und der galvanischen Kupferprozesse

- Laserbohrungsdurchmesser zwischen 80-100µm

- Dicke des Dielektrikums zwischen 60-80µm

- Auch bei optimalem Bohrdurchmesser verbleibt die Möglichkeit einer kleinen Mulde (Vertiefung) von wenigen µm auf dem gebohrten Pad, wie im Bild oben zu sehen

Eine kurze Übersicht der Prozessschritte des „Copper Vias Filling“-Prozesses:

- Die Chemie besteht aus einem speziellen Mischungsverhältnis zwischen Aufhellern und Nivelliermitteln, mit denen die Hohlräume des Sacklochs (Blind Hole) gefüllt werden

- Die Aufheller (brightener) wirken auf den Boden und beschleunigen die Kupferabscheidung

- Der Nivellierer (leveler) verhindert Ablagerungen auf der Oberfläche und ermöglicht eine ausreichende Planarität zum Verlöten von „Via-in-Pads“.

Auswahl des Basismaterials

Die Auswahl des optimalen Basismaterials unter Berücksichtigung der wichtigsten Parameter ist essentiell:

- Tg – Glass Transition Temperature

- CTE – thermal coefficient of Z axis expansion

- Td – Decomposition temperature

Tg – Zu den bekanntesten Parametern der Materialspezifikation zählt der Tg-Wert. Der Wert von Tg ist die Temperatur, bei der das Material (Laminat) vom starren Zustand (wie Glas) in ein plastischeres Verhalten übergeht (Glasübergangstemperatur). Dieser Wert ist wichtig, da sich die Material-Eigenschaften bei Temperaturen über dem Tg ändern und verschlechtern.

CTE– Der Wärmeausdehnungskoeffizient, beschreibt die Ausdehnung des Basismaterials bei Temperatur-erhöhung, primär in z-Achse, und erhöht sich typischerweise signifikant bei Temperaturen über Tg. Bei hohen CTE-Werten gemäß Spezifikation im Materialartenblatt, insbesondere über Tg, besteht wegen der schnelleren thermischen Ausdehnung ein erhöhtes Ausfallrisiko der bestückten Baugruppe. Materialien können den gleichen Tg-Wert haben, jedoch mit unterschiedlichem CTE. Hier ist es vorteilhaft das Material mit gleichem Tg aber niedrigem CTE-Wert zu wählen.

Td – Die Zersetzungstemperatur ist ein Maß für den Abbau des Materials. Die analytische Methode misst die Temperatur, bei der das Material 5% seiner Masse verliert. An diesem Punkt ist die Zuverlässigkeit beeinträchtigt und Delaminationsphänomene können auftreten. Für hohe Zuverlässigkeitsanforderungen der Leiterplatte ist ein Wert von Td ≥ 340 ℃ erforderlich.

Für weitere Informationen zur HDI-Technologie wenden Sie sich bitte an Ihr lokales NCAB-Team. Wir helfen Ihnen jederzeit gerne weiter.

Design guidelines for HDI

Download our PCB design guidelines for HDI to get your design right from start.